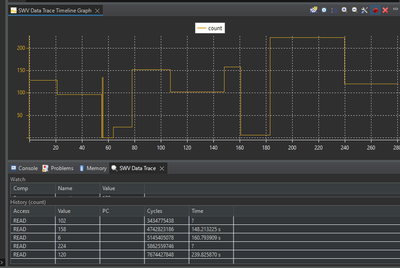

Resolved! SWV doesn't display the right information

Hi!! To test how the SWV data trace timeline graph works, I have a simple application where I increment by 1 a variable called count. Very basic. In debug mode, I see count increasing correctly in the live expressions window. while(1){ count++; HAL_D...