STM32 MCUs Products

Ask questions, find answers, and share insights on STM32 products and their technical features.

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Mark all as New

- Mark all as Read

- Float this item to the top

- Subscribe

- Bookmark

- Subscribe to RSS Feed

- Invite a Friend

- Threaded format

- Linear Format

- Sort by Topic Start Date

Forum Posts

Is there a display to be connected on nucleo 64

Hi good people. I would love to try a display connected to my stm32F411RE. But I cant find any product. Do you know any? thx a lot. Greetings. Jan

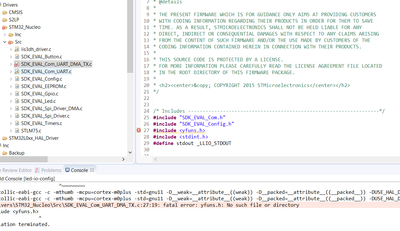

I am trying to run the S2-lp SDK example project on truestudio but i am running in so many errors? and missing files?

I am trying to run the S2-lp SDK example project on truestudio but I am running in so many errors. one of them is that the yfuns.h file is not even the directories.

Inter Byte Delay while sending Bootloader commands on STM32f030xC

Dear All,Currently we're using STM32F030CC micro controller to make a programmer which will program STM32F030CC serially via UART Bootloader commands.First we verified / noted the response of every command by sending each command via serial monitor.T...

Is there a Bluetooth HCI library for STM32F7 ?

Hi, I need to interface STM32F7 with a Bluetooth chipset that supports HCI interface over UART/USB. I would like to know if STM32CubeMX provides such a library or is there any other library available that can be used ? Any direction in this regard ...

How to wake-up from sleep-mode on STM32L072

I've modified the AT-command example from the X-CUBE-SFOX package to add another serial interface as a command link.Now you can enter AT-commands via LPUART1 connected to terminal program on PC or send them from another CPU via USART1 and forward the...

DFU USB disabling.

Please tell me how to disable the DFU USB in application code.

Low Power Mode disable

How to disable the low power mode of stm32l072 controller.

Problem using STM32F769-Discovery with STM32CubeMX 4.27

I've got a few problems when creating a simple project using STM32CubeMX :1) using all the default setting by STM32CubeMX and clicked YES to "initialize all peripherals with their default MODE", the LED ports were default to input mode ! Weird ! If s...

-

STM32F4 Series

5,907 -

STM32H7 series

5,602 -

STM32L4 series

3,039 -

TIM

2,970 -

ADC

2,912 -

DMA

2,747 -

UART-USART

2,675 -

STM32F1 Series

2,212 -

STM32F7 series

2,169 -

SPI

2,141 -

STM32G4 Series

1,595 -

STM32F0 Series

1,584 -

STM32G0 Series

1,451 -

I2C

1,383 -

Flash

1,342 -

Documentation

1,305 -

STM32L0 Series

1,281 -

GPIO-EXTI

1,210 -

STM32F3 Series

1,195 -

Power

1,153 -

STM32U5 series

1,138 -

CAN

1,071 -

RTC

918 -

Interrupt

893 -

RCC

768 -

Debug

663 -

STM32H5 series

658 -

USB

591 -

QSPI

556 -

SDIO-SDMMC

551 -

FMC-FSMC

542 -

STM32CubeMX

516 -

STM32L1 Series

460 -

FDCAN

411 -

DAC

409 -

Bug-report

378 -

STM32F2 Series

347 -

OctoSPI

282 -

STM32L5 Series

277 -

I2S

268 -

Bootloader

251 -

RAM

243 -

STM32C0 Series

241 -

IWDG-WWDG

209 -

STM32N6 series

209 -

HRTIM

200 -

SAI

176 -

SysTick

154 -

STM32U0 Series

135 -

LPTIM

131 -

LPUART

123 -

BLE

121 -

DSP

119 -

STM32CubeIDE

107 -

COMP

86 -

RESET

84 -

LCD-LTDC

74 -

DFSDM

68 -

TSC

62 -

I3C

60 -

SDADC

55 -

Ethernet

54 -

OPAMP

54 -

ST boards

51 -

FlashLoader

50 -

Wifi

37 -

UCPD

37 -

Modbus

32 -

STM32U3 Series

24 -

ST-Link

22 -

XSPI

20 -

MDF

18 -

STM32Cube MCU packages

17 -

PSSI

16 -

STM32CubeProgrammer

13 -

CORDIC

13 -

DCMI

12 -

EMC

11 -

Others

10 -

Legacy products

8 -

Hardware components

7 -

TouchGFX

6 -

Power Supply Management

6 -

STM32C5 series

6 -

Other Tools

5 -

ST-Boards

4 -

SW4STM32

4 -

Other software

4 -

Protection and signal conditioning

3 -

OpenSTLinux

3 -

STM32CubeExpansion

3 -

STM32 Motor Control

2 -

SVD

2 -

Other boards

2 -

Schematic

2 -

X-LINUX-AI

2 -

Other hardware

2 -

STM32N6

2 -

STM32V8 Series

2 -

Low Power RF Solutions

1 -

LoRa

1 -

FatFS

1 -

Microphones

1 -

CMSIS

1 -

Zephyr

1 -

CRC

1 -

DSI

1 -

Suggestion

1 -

Error

1 -

Need improvement

1 -

USB Type-C and Power Delivery

1 -

STM32 Security

1 -

U-Boot

1 -

RTC and TimeKeeper

1 -

MCSDK6

1 -

Discontinued

1 -

FOC

1 -

MC Workbench

1 -

Power management Design center

1 -

MEMS-Studio

1 -

Tools

1 -

Neural-ART Accelerator

1 -

HAL

1