- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeIDE (MCUs)

- I am getting UNALIGNED HardFault (attempt to perfo...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

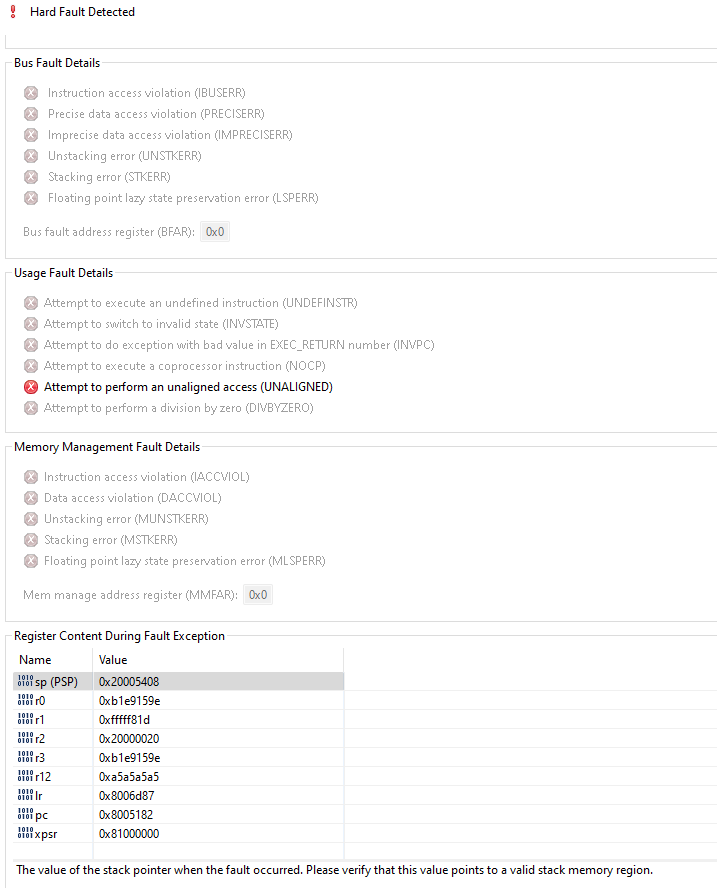

I am getting UNALIGNED HardFault (attempt to perform an unaligned access) on ldr.w and blx.w instructions (as seen in disassembly when debugging). I am using STM32CubeIDE with the standard toolchain for stm32 (arm gcc, Thumb2).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-01-19 12:00 AM

I am importing a library (which I am also building with the same toolchain), in which the errors are occuring.

Can I tell the compiler to not create unaligned addresses? Or do I have to change the source code of the library?

I have tried compiling with -mno-unaligned-access.

- Labels:

-

DEBUG

-

STM32CubeIDE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-01-19 03:44 AM

> Can I tell the compiler to not create unaligned addresses?

Cortex-M-specific toolchains tend to come with settings which do generate aligned addresses. Howevr, you can't generally prevent the *user* to generate unaligned address accesses. simply by some pointer juggling.

Debug the hardfault in the usual way (walk back manually through mixed-C-disasm while observing registers' content) to find out exactly what source lines caused the unaligned access. Post it here for further discussion.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-12-06 07:01 AM

Hi, I am getting the same hard fault while using lwIP and Ethernet with STM32F746G DISC board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-12-06 10:40 AM

And @Community member 's answer still applies. See what code is that the given PC address and see if you can determine why it generated the fault.

Generally the F7 supports unaligned access except for LDM, STM, LDRD and STRD instructions. There is a bit in the CCR register that can enable unaligned access faults when they otherwise might be allowed. See PM0253.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-12-06 10:45 AM

Show the actual code that's faulting, the registers, and the instructions.

It should be more apparent as to what's going on.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-12-09 08:43 AM

Hi, I attached my project for review I am just trying to ping my board but I don't see any response. I set up the Rx,/Tx_Descrip and Rx/Tx_Buf in SRAM1 region. Above that I give access to lwIP_Heap Memory. Please check and make it functional. Code is running but no response from board. II am using STMCubeIDE 1.6.1 with CubeMX 1.6.2

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-12-09 08:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-02 04:42 AM

I need to parse incoming packets with structure like

{

uint8_t packet_id;

uint16_t packet_CRC;

uing8_t var1;

double var2;

...

}For M7 core (STM32H755) CubeIDE make code that generates "unaligned access" hard fault on simple access of unaligned variables like

IncomePacked.packet_CRC = calculated_CRC;

double MyVar = IncomePacked.var2, etc.

I have need to add "-mno-unaligned-access" compiler option to rid that faults.

Strange, but M4 core works OK with the same code without additional options.

- ARM7 and linux compatibiilty of STM32CubeIDE in 2025 (e.g. Raspberry Pi) in STM32CubeIDE (MCUs)

- CubeMX setting incorrect baudrate for STM32WL33CC LPUART in STM32CubeMX (MCUs)

- "Could not determine GDB version" in STM32CubeIDE on Kali Linux in STM32CubeIDE (MCUs)

- STM32CubeIDE on MacBook (M3 Max) won't recognize NUCLEO-F446RE in STM32CubeIDE (MCUs)

- Pretty Printers for STL containers on MacOS? (Can't view STL container contents in the debugger) in STM32CubeIDE (MCUs)