- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- STM32H7 RMII timing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H7 RMII timing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-18 9:17 AM

Hello,

We are using STM32H743ZIT6 revision V.

This is connected to an ethernet PHY device via RMII. The PHY outputs the 50MHz RMII REFCLK to drive the RMII on the STM.

According to the following sources, the RMII TX data lines (TXD0 and TXD1) should be sampled by the PHY on the rising edge of the REFCLK, and thus should transition around the falling edge:

- official RMII spec

- STM32H7 datasheets Table 112. Dynamics characteristics: Ethernet MAC signals for RMII

- the timing diagrams from the PHY

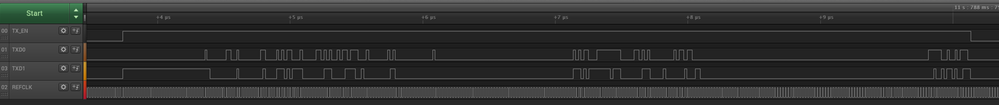

This is not what I am seeing. The STM seems to be transitioning the TX data lines on (or near) the rising edge of REFCLK. We are getting CRC errors detected at the PHY on the RMII interface side.

The trace attached shows a packet going out on the RMII. The scope resolution is 2ns, so it's possible the data lines do transition just before the clock edge, but according to the timing diagrams the transition should be at least 2ns before a clock rising edge.

Any idea how to solve this? I didn't manage to find a way to invert the clock at either end (PHY or STM). The PHY supports RGMII clock delay, but only on RGMII, not RMII.

Thanks, Kieran.

Solved! Go to Solution.

- Labels:

-

Ethernet

-

GPIO-EXTI

-

STM32CubeMX

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-18 10:00 AM

don't you just love those posts where you figure out a solution right after posting...

Changing the drive strength on the TXD0, TXD1 and TX_EN signals to HIGH (they default to LOW from cubeMX) seems to push the timing into bounds, and the CRC errors on the PHY are gone.

Hopefully that may help someone else...

Thanks, Kieran.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-18 10:00 AM

don't you just love those posts where you figure out a solution right after posting...

Changing the drive strength on the TXD0, TXD1 and TX_EN signals to HIGH (they default to LOW from cubeMX) seems to push the timing into bounds, and the CRC errors on the PHY are gone.

Hopefully that may help someone else...

Thanks, Kieran.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-18 10:51 AM

https://www.st.com/resource/en/datasheet/stm32h743zi.pdf

Table 63 suggests that in a typical case medium speed is the most appropriate one. I'm using medium speed for RMII pins on multiple F7 based boards without problems. Also take a note that at these speeds the measurement probe can distort the signal and what you see could not be the original signal without probe.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-18 11:39 AM

Way the universe works I think....

Also on H7 watch that the compensation cell is enabled.

/*

Note : The activation of the I/O Compensation Cell is recommended with communication interfaces

(GPIO, SPI, FMC, QSPI ...) when operating at high frequencies(please refer to product datasheet)

The I/O Compensation Cell activation procedure requires :

- The activation of the CSI clock

- The activation of the SYSCFG clock

- Enabling the I/O Compensation Cell : setting bit[0] of register SYSCFG_CCCSR

To do this please uncomment the following code

*/

/*

__HAL_RCC_CSI_ENABLE() ;

__HAL_RCC_SYSCFG_CLK_ENABLE() ;

HAL_EnableCompensationCell();

*/

Up vote any posts that you find helpful, it shows what's working..

- I2C Not Working in STM32CubeIDE (MCUs)

- STM32CubeMX STM32H7 Ethernet MAC Initialization is Broken in STM32CubeMX (MCUs)

- Enabling Ethernet Interface on Nucleo-H743ZI2 in STM32CubeMX (MCUs)

- STM32CubeMX STM32H7 I2C Custom Timing not so Custom. in STM32CubeMX (MCUs)

- STM32H7: Why does the first call to HAL_MMC_WriteBlocks_DMA take so long to return? in STM32CubeIDE (MCUs)