- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Re: STM32G474RE ADC Clocking

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G474RE ADC Clocking

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-09 06:19 AM

Hiya!

I'm trying to figure out the clock config for my micro. I'm using ADC3 IN1 currently, and using the internal HSI clock source. Using the default settings, I can't seem to get anything better than 3.3 MSPS, and this is with a 10-Bit ADC resolution. From what I read, I should be able to get around 4 to 5 MSPS!

However, that's assuming the ADC is clocked at 60 MHz. By defualt, the ADC clock is divided by 4, so the resulting clock is at 42.5 MHz. Okay! So, I just need to change the divider ratio/or clock it to the PLLP to fix this.

However, I can't figure out a good way to get the prescaler to be okay with an async clock mode with a divider less than 4.

I've tried changing the PLLP clock divider ratio down to 6, which gives the ADC a clock of 56.666667. Won't let me change the prescaler still, stuck at async divide by 4.

Tried a PLLP clock divider of 5, which gives 68 MHz. Still can't change it to lower than 4.

And changing the PLLP clock DOES impact my performance; I can change my trigger timer value and see my maximum sample speed change. If I manually change this line of code,

hadc3.Init.ClockPrescaler = ADC_CLOCK_ASYNC_DIV4;

to lower divider values, it works as expected, and I get the higher sampling rates I want.

Why is CubeMX throwing a fit about this?

Using STM32CubeIDE 1.14.0. STM32G474-DPOW board.

- Labels:

-

STM32CubeIDE

-

STM32CubeMX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-09 07:01 AM

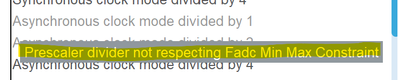

Hover over the grayed out selection to understand the error.

In this case, it looks like CubeMX is using SYSCLK to determine this constraint regardless of the setting of the ADC345 clock mux.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-09 10:13 AM

Is this intentional? I'm not sure if I'm just misunderstanding how clocking the ADC works or if this is a bug. :thinking_face:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-09 10:43 AM

No, it's almost certainly a bug. Perhaps @Semer CHERNI or @Amel NASRI can confirm or investigate.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-10 08:08 AM - last edited on 2024-01-11 06:01 AM by Amel NASRI

Hello @Jbin0101

First let me thank you for posting.

After investigating the situation, I found that @TDK is right about the fact that CubeMX is using the SYSCLK.

The issue is now raised internally for further analysis (170481: this is an internal ticket reference)

In the mean while you can change the divider value manually in the generated code to suite your need.

KR,

Semer.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-07-31 03:26 PM

Hello @Semer CHERNI and company; any updates with this?

The issue was first reported in January, it is now last day of July. I have the latest version of CubeIDE (1.16.0) and the built-in MX will not allow me to change ADC345 Clock Mux. This looks like the same bug that @Jbin0101 had.

Is there an ETA for when this will be patched?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-07-31 03:39 PM - edited 2024-07-31 03:40 PM

This is not the same issue as the OP.

To change the ADC345 mux, you first need to enable one of those ADCs. If that doesn't work, open up a new thread with relevant information and attach the IOC file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-07-31 10:51 PM

@TDK Copy that - so has internal ticket reference # 170481 received any updates that can be shared, or has the ticket been closed/resolved?

Regarding the issue I mentioned, yes, I have had ADC3, ADC4, and ADC5 active in my project. So I will open another thread as you suggested.

- H5 ADC clock in STM32CubeIDE (MCUs)

- STM32H5xx - CUBE MX 6.13 - Error activating RTC Clock source for Backup register access in STM32CubeMX (MCUs)

- Clock Configuration -> Reset Clock Configuration in STM32CubeIDE (MCUs)

- STM32CubeMX Improvement idea: Clock Configuration (clock tree) in STM32CubeMX (MCUs)

- STM32H755: Wrong RCC clock auto configuration in STM32CubeMX (MCUs)