- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeIDE (MCUs)

- Re: SFR Register View for RTC backup registers is ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SFR Register View for RTC backup registers is using wrong address

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-13 6:29 AM

Processor: STM32F103

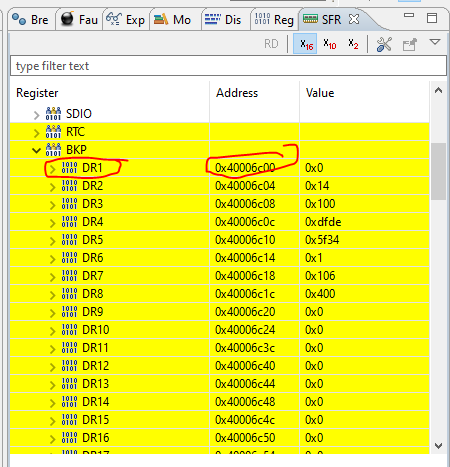

Using the SFR view in STM32CubeIDE, address 0x40006c00 is used for Register DR1;

looking into the software implementation this is actually 4 bytes before the DR1 register, resulting in a shift of DRx register by one.

Also according RM0008 the first 4 bytes based on above offset are reserved.

RN0114 (release notes for STM32CubeIde) are not mentioning this topic.

Implementation with HAL (for DR1 value 1 is handed as BackupRegister, resulting in an offset of 4 Bytes) :

uint32_t HAL_RTCEx_BKUPRead(RTC_HandleTypeDef *hrtc, uint32_t BackupRegister)

{

uint32_t backupregister = 0U;

uint32_t pvalue = 0U;

/* Prevent unused argument(s) compilation warning */

UNUSED(hrtc);

/* Check the parameters */

assert_param(IS_RTC_BKP(BackupRegister));

backupregister = (uint32_t)BKP_BASE;

backupregister += (BackupRegister * 4U);

- Labels:

-

RTC

-

STM32CubeIDE

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-13 11:05 AM

Similar: https://community.st.com/s/question/0D50X0000ALwiivSQB/stm32f107-bkp

@Imen DAHMEN , can this please be fixed?

Thanks,

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-19 2:47 AM

Hi,

Thank you for the feedback!

We take note of this and will be fixed asap.

-Imen

- All IRQ handler not called when using STM32F107VCT in STM32CubeIDE (MCUs)

- Problem of writing to opposite registers at the same time. in STM32CubeIDE (MCUs)

- STM32U073/083 I2C4, not visible in SFR view in STM32CubeIDE (MCUs)

- STM32CubeIDE in combination STM32H7Rx/7Sx some errors/bugs? in STM32CubeIDE (MCUs)

- WRP2A and WRP2B registers are not showing on the SFRs tab in STM32CubeIDE (MCUs)