STM32H745I-Disco crash at SystemClock_Config

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-12 4:23 AM

I have a STM32H745I-Disco board which is still not supported. If I use an STM32H750B-DK example from TouchGFX (same board except mcu) I can download it from the designer and run it on the board. When I move the code to CubeIDE I can compile and download the code from CubeIDE. After reset with the Ex_Mem_Boot programmed in flash I can reach main. Stepping through the code it seems to crash at

ret = HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_4); when it enables the sys clock.

Martin any idea?

How long away are we to have the heavily advertised STM32 tool set supporting all mcu's? :)

Solved! Go to Solution.

- Labels:

-

RCC

-

STM32CubeIDE

-

STM32H7 Series

-

TouchGFX

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-12 5:40 AM

This should work

//****************************************************************************

/**

* @brief System Clock Configuration

* The system Clock is configured as follow :

* System Clock source = PLL (HSE)

* SYSCLK(Hz) = 400000000 (Cortex-M7 CPU Clock)

* HCLK(Hz) = 200000000 (Cortex-M4 CPU, Bus matrix Clocks)

* AHB Prescaler = 2

* D1 APB3 Prescaler = 2 (APB3 Clock 100MHz)

* D2 APB1 Prescaler = 2 (APB1 Clock 100MHz)

* D2 APB2 Prescaler = 2 (APB2 Clock 100MHz)

* D3 APB4 Prescaler = 2 (APB4 Clock 100MHz)

* HSE Frequency(Hz) = 25000000

* PLL_M = 5

* PLL_N = 160

* PLL_P = 2

* PLL_Q = 4

* PLL_R = 2

* VDD(V) = 3.3

* Flash Latency(WS) = 4

* @param None

* @retval None

*/

static void SystemClock_Config(void)

{

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

/*!< Supply configuration update enable */

HAL_PWREx_ConfigSupply(PWR_DIRECT_SMPS_SUPPLY);

/* The voltage scaling allows optimizing the power consumption when the device is

clocked below the maximum system frequency, to update the voltage scaling value

regarding system frequency refer to product datasheet. */

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1); /* SCALE0 for 480 MHz */

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {}

/* Enable HSE Oscillator and activate PLL with HSE as source */

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.HSIState = RCC_HSI_OFF;

RCC_OscInitStruct.CSIState = RCC_CSI_OFF;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 5;

RCC_OscInitStruct.PLL.PLLN = 160;

RCC_OscInitStruct.PLL.PLLFRACN = 0;

RCC_OscInitStruct.PLL.PLLP = 2;

RCC_OscInitStruct.PLL.PLLR = 2;

RCC_OscInitStruct.PLL.PLLQ = 4;

RCC_OscInitStruct.PLL.PLLVCOSEL = RCC_PLL1VCOWIDE;

RCC_OscInitStruct.PLL.PLLRGE = RCC_PLL1VCIRANGE_2;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler(__FILE__, __LINE__);

}

/* Select PLL as system clock source and configure bus clocks dividers */

RCC_ClkInitStruct.ClockType = (RCC_CLOCKTYPE_SYSCLK | RCC_CLOCKTYPE_HCLK | RCC_CLOCKTYPE_D1PCLK1 | RCC_CLOCKTYPE_PCLK1 | \

RCC_CLOCKTYPE_PCLK2 | RCC_CLOCKTYPE_D3PCLK1);

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.SYSCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB3CLKDivider = RCC_APB3_DIV2;

RCC_ClkInitStruct.APB1CLKDivider = RCC_APB1_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_APB2_DIV2;

RCC_ClkInitStruct.APB4CLKDivider = RCC_APB4_DIV2;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_4) != HAL_OK)

{

Error_Handler(__FILE__, __LINE__);

}

/*

Note : The activation of the I/O Compensation Cell is recommended with communication interfaces

(GPIO, SPI, FMC, QSPI ...) when operating at high frequencies(please refer to product datasheet)

The I/O Compensation Cell activation procedure requires :

- The activation of the CSI clock

- The activation of the SYSCFG clock

- Enabling the I/O Compensation Cell : setting bit[0] of register SYSCFG_CCCSR

To do this please uncomment the following code

*/

/*

__HAL_RCC_CSI_ENABLE() ;

__HAL_RCC_SYSCFG_CLK_ENABLE() ;

HAL_EnableCompensationCell();

*/

}

//****************************************************************************Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-12 5:40 AM

This should work

//****************************************************************************

/**

* @brief System Clock Configuration

* The system Clock is configured as follow :

* System Clock source = PLL (HSE)

* SYSCLK(Hz) = 400000000 (Cortex-M7 CPU Clock)

* HCLK(Hz) = 200000000 (Cortex-M4 CPU, Bus matrix Clocks)

* AHB Prescaler = 2

* D1 APB3 Prescaler = 2 (APB3 Clock 100MHz)

* D2 APB1 Prescaler = 2 (APB1 Clock 100MHz)

* D2 APB2 Prescaler = 2 (APB2 Clock 100MHz)

* D3 APB4 Prescaler = 2 (APB4 Clock 100MHz)

* HSE Frequency(Hz) = 25000000

* PLL_M = 5

* PLL_N = 160

* PLL_P = 2

* PLL_Q = 4

* PLL_R = 2

* VDD(V) = 3.3

* Flash Latency(WS) = 4

* @param None

* @retval None

*/

static void SystemClock_Config(void)

{

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

/*!< Supply configuration update enable */

HAL_PWREx_ConfigSupply(PWR_DIRECT_SMPS_SUPPLY);

/* The voltage scaling allows optimizing the power consumption when the device is

clocked below the maximum system frequency, to update the voltage scaling value

regarding system frequency refer to product datasheet. */

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1); /* SCALE0 for 480 MHz */

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {}

/* Enable HSE Oscillator and activate PLL with HSE as source */

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.HSIState = RCC_HSI_OFF;

RCC_OscInitStruct.CSIState = RCC_CSI_OFF;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 5;

RCC_OscInitStruct.PLL.PLLN = 160;

RCC_OscInitStruct.PLL.PLLFRACN = 0;

RCC_OscInitStruct.PLL.PLLP = 2;

RCC_OscInitStruct.PLL.PLLR = 2;

RCC_OscInitStruct.PLL.PLLQ = 4;

RCC_OscInitStruct.PLL.PLLVCOSEL = RCC_PLL1VCOWIDE;

RCC_OscInitStruct.PLL.PLLRGE = RCC_PLL1VCIRANGE_2;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler(__FILE__, __LINE__);

}

/* Select PLL as system clock source and configure bus clocks dividers */

RCC_ClkInitStruct.ClockType = (RCC_CLOCKTYPE_SYSCLK | RCC_CLOCKTYPE_HCLK | RCC_CLOCKTYPE_D1PCLK1 | RCC_CLOCKTYPE_PCLK1 | \

RCC_CLOCKTYPE_PCLK2 | RCC_CLOCKTYPE_D3PCLK1);

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.SYSCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB3CLKDivider = RCC_APB3_DIV2;

RCC_ClkInitStruct.APB1CLKDivider = RCC_APB1_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_APB2_DIV2;

RCC_ClkInitStruct.APB4CLKDivider = RCC_APB4_DIV2;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_4) != HAL_OK)

{

Error_Handler(__FILE__, __LINE__);

}

/*

Note : The activation of the I/O Compensation Cell is recommended with communication interfaces

(GPIO, SPI, FMC, QSPI ...) when operating at high frequencies(please refer to product datasheet)

The I/O Compensation Cell activation procedure requires :

- The activation of the CSI clock

- The activation of the SYSCFG clock

- Enabling the I/O Compensation Cell : setting bit[0] of register SYSCFG_CCCSR

To do this please uncomment the following code

*/

/*

__HAL_RCC_CSI_ENABLE() ;

__HAL_RCC_SYSCFG_CLK_ENABLE() ;

HAL_EnableCompensationCell();

*/

}

//****************************************************************************Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-14 6:28 PM

Hi, thanks for your help.

PWR_DIRECT_SMPS_SUPPLY was part of the solution. STM32H745 with PWR_LDO_SUPPLY does not startup properly during a power cycle and gets bricked.

I furthermore had omitted syscalls.c and sysmem.c. That caused the crashes at startup. I converted the project to the STM32H745 and STM32CubeIDE happily builds CM7 part of it. I can run now TouchGFX. I would like to build also code for the CM4 but CubeIDE is not up it yet. I tried SystemWorkbench but found it very buggy.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-14 7:20 PM

I think most are using IAR or Keil

For GNU/GCC I'd just use make

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-14 6:14 PM

In related news

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-09 2:14 AM

Hi

unfortunately, I Have same issue. I test both PWR_EXTERNAL_SOURCE_SUPPLY and PWR_LDO_SUPPL. of course, PWR_LDO_SUPPLY is the proper option. In both conditions debug crashes when the code reaches to SystemClock_Config.

I use CubeMX 6.7.0

I change

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);

to __HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE2);

and the problem is solved. I don't understand the reason.

is it true the way that I did?

another problem is that PWR_REGULATOR_VOLTAGE_SCALE2 doesn't exist in cubeMX so I have to adjust the config after each code generation.

Also, I faced with a crash when the code reach to MX_LTDC_Init function.

any Idea?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-09 2:27 AM

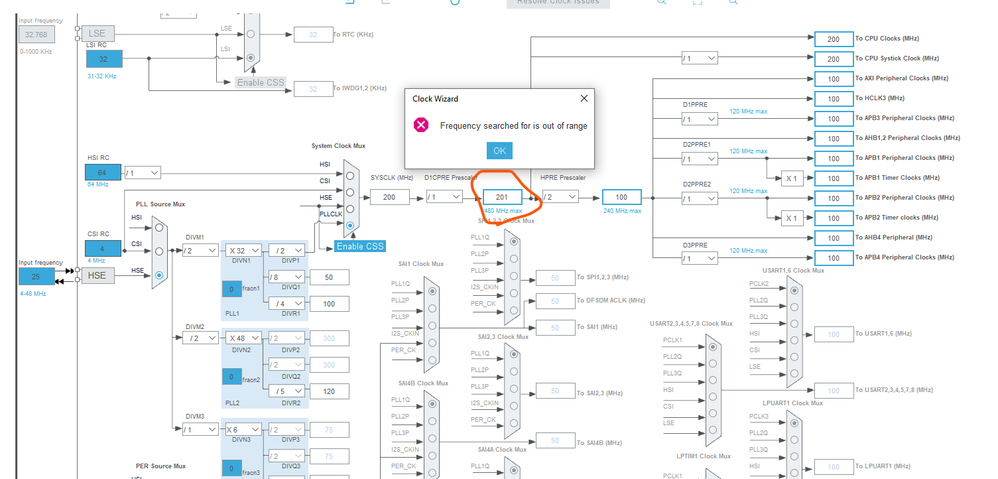

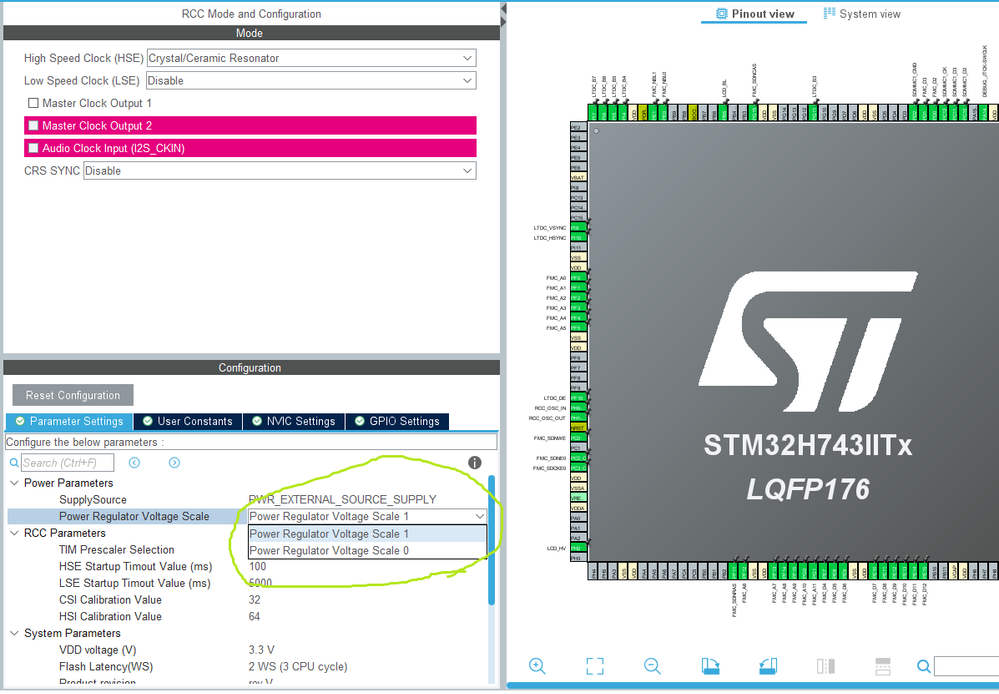

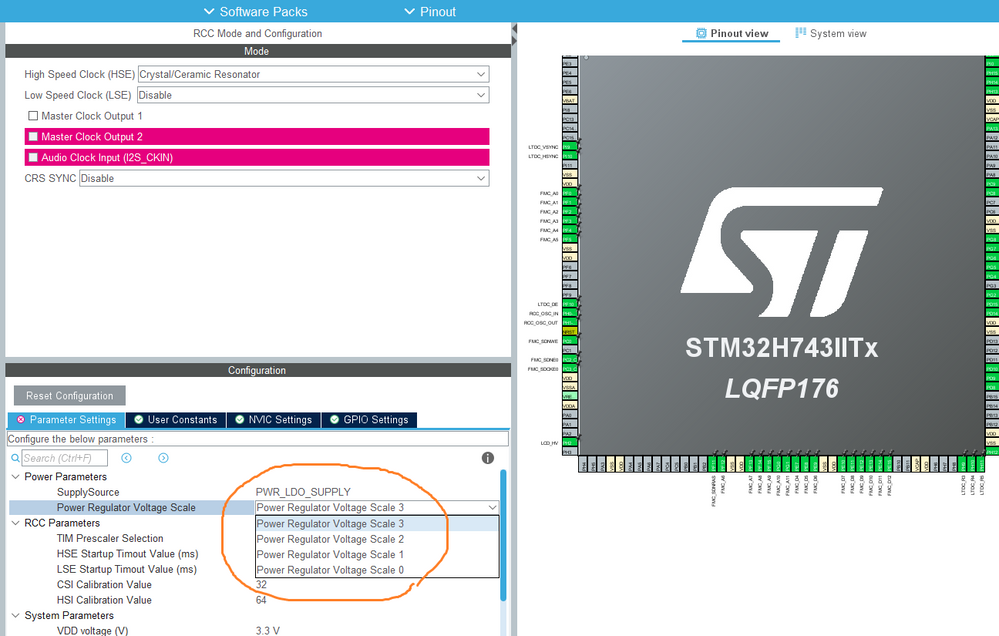

also, I create two different cubeMX files and encounter two different menu

also, the clock configuration doesn't get a clock speed of more than 200Mhz. I attached an image to clarify problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-09 5:23 PM

That is definitely strange. Could you create a new post about your issue to have more visibility ?

Can you confirm the two projects are created from scratch and have the same configurations but show different options now.only for the power voltage scale.

/Romain

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-19 2:02 PM

The value of the "SupplySource" setting differs in those same screenshots... And the "Product revision" setting also has an impact on the maximum frequencies.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-01 7:00 AM

Hi, I've just experienced a simillar problem. In my case, Cube generated RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV1; instead of RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2; I have been quite intensively playing around with everything so it probably went mad. After clicking correct values to clock configurator once again and pressing alt+K to force code generation, the problem was solved.