- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Why there is a 1bit shift in MOSI with respect...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

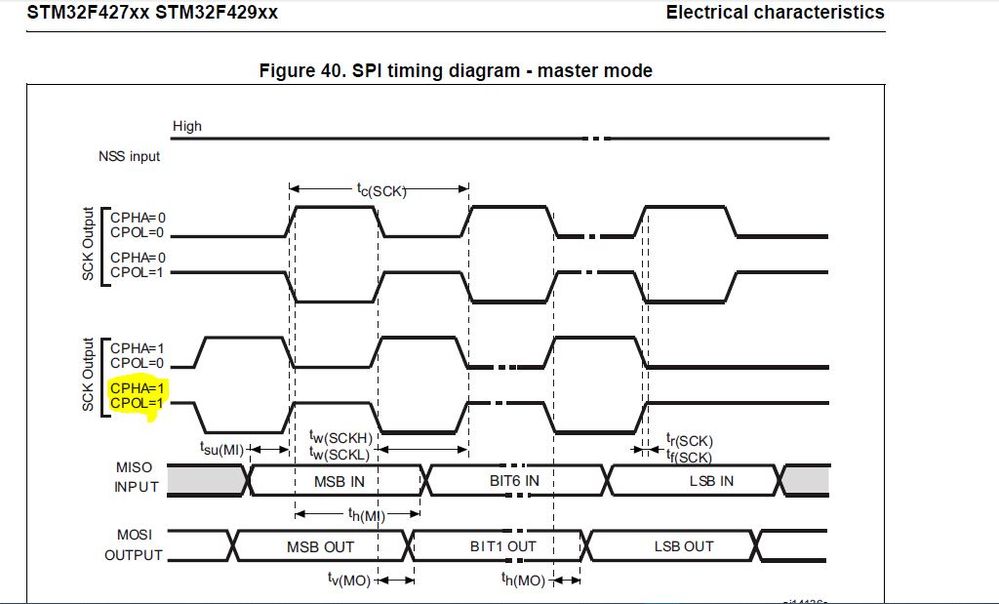

Why there is a 1bit shift in MOSI with respect to the clock of spi in stm32f429zi discovery board?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 05:39 AM

I am using stm32f429zi discovery board.

When I am trying to use SPI peripheral, one bit shift in MOSI is observed with respect to Clock.

It is tested in all modes of SPI, still getting the same result in oscilloscope. We are not able to understand this behaviour of SPI.

- Labels:

-

SPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 07:05 AM

Master? Slave? What is the content of SPI registers for the displayed picture, and what data are you trying to transfer?

If you've set SCK to highest OSPEEDR setting, switch to slower; if you've set it to slowest, switch to higher.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 07:32 AM

Clock Edge used...

- SPI ICs may clock in and out on different clock edges (rising, falling).

- If data out changed on clock rising edge, you likely want to clock in on clock falling edge, in centre of bit, after bit has stabilized (or even next rising edge).

- Many CPUs allow you to configure what edges to clock data in/out on so you can match to many ICs without needing inverters on clock signals.

- Check your STM32CubeMX settings for SPI for clock edge used.

- If you clock in and out on same edge you'll be clock in at data transition = may get garbage input.

Paul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 07:54 AM

Check clock phase settings, show initialization code.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 08:06 AM

We have tried with both clock phase rising and falling. The device configured is as master.

In this figure the data transferred is 1 bit i.e. 0x45.

The spi clock frequency set is 350 khz

Here in this figure, we can there is shift of 1 bit. i.e. data transferred is 0xA2.

We have made TI mode disable still the waveform we are getting is likely to be the data transferred in TI mode as per datasheet.

What could be the reason behind this data shift?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 08:06 AM

Can you please explain or elaborate this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 08:20 AM

The delay between edges is suspicious, as if that picture would show waveforms from two different SPIs... which pins are we talking about? Are there other SPIs active on that board?

Prepare a minimal but complete compilable program exhibiting the problem and post.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 01:23 PM

Hello

for CPHA=1 and CPOL=1 the captured image does not have any bit shift.

Revise the use of pullups or pulldowns resistors (if exist) to fit with clock polarity and the other signals

check SPI registers if have the values that initialization code set.

- Start of DMA -SPI slave transmission frame is not in sync with Master's Slave Select line assertion in STM32 MCUs Products

- Configuring STemWin in stm32f429zi discovery in STM32 MCUs TouchGFX and GUI

- Issue on Stm32F429ZI Discovery Board STlink for External Programming/Debugging in STM32 MCUs Boards and hardware tools

- Has issue on a project to use FileX to access SD card on stm32f429zi Nucleo board in STM32 MCUs Products

- Firmware download via Y-Modem crashes with the following error when selected in UserApp example project "!!Error during file download!!". in STM32 MCUs Security