- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32H743 Parallel synchronous transmission wi...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H743 Parallel synchronous transmission with DMA and GPIO

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 03:53 AM

Hi all,

I have problem to get work stm32h743 as parallel synchronous transmission with DMA and 16bits GPIO and timer as clok. I need something like in Application note AN4666 but for H7xx.

I'm using GPIO port E what is on AHB4 and it si D3 domain and Timer 1 chanel 1 pwm output as clok. TIM1 is on APB2

pwm is running but i don't get any data from Port E

here is some documentation what i going through but no success .

en.DM00306681, en.DM00387108, RM0433

I'm using SW4STM32 and HAL lib.

Any advice ?

Thank you

In main()

if(enable == 1){

SCB_CleanInvalidateDCache();

HAL_DMA_Abort(htim1.hdma[TIM_DMA_ID_CC1]);

HAL_DMA_DeInit(htim1.hdma[TIM_DMA_ID_CC1]);

MX_DMA_Init();

MX_TIM1_Init();

/* USER CODE BEGIN 2 */

//HAL_TIM_PWM_Start(&htim2, TIM_CHANNEL_1);

htim1.hdma[TIM_DMA_ID_CC1]->XferCpltCallback = TransferComplete;

htim1.hdma[TIM_DMA_ID_CC1]->XferErrorCallback = TransferError;

if (HAL_DMA_Start_IT(htim1.hdma[TIM_DMA_ID_CC1], (uint32_t)&asrc_buffer, (uint32_t)&(GPIOE->ODR), FULL_FRAME_SIZE) != HAL_OK)

{

/* Transfer Error */

Error_Handler();

}

__HAL_DMA_DISABLE_IT(htim1.hdma[TIM_DMA_ID_CC1], DMA_IT_HT);

__HAL_TIM_ENABLE_DMA(&htim1, TIM_DMA_CC1);

/*Start TIM PWM channel 1 */

if (HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_1) != HAL_OK)

{

//PWM Generation Error

Error_Handler();

}

enable = 0;

HAL_Delay(500);

}

init

void HAL_TIM_PWM_MspInit(TIM_HandleTypeDef* htim_pwm)

{

if(htim_pwm->Instance==TIM1)

{

/* USER CODE BEGIN TIM1_MspInit 0 */

/* USER CODE END TIM1_MspInit 0 */

/* Peripheral clock enable */

__HAL_RCC_TIM1_CLK_ENABLE();

/* TIM1 DMA Init */

/* TIM1_CH1 Init */

hdma_tim1_ch1.Instance = DMA2_Stream6;

hdma_tim1_ch1.Init.Request = DMA_REQUEST_TIM1_CH1;

hdma_tim1_ch1.Init.Direction = DMA_MEMORY_TO_PERIPH;

hdma_tim1_ch1.Init.PeriphInc = DMA_PINC_DISABLE;

hdma_tim1_ch1.Init.MemInc = DMA_MINC_ENABLE;

hdma_tim1_ch1.Init.PeriphDataAlignment = DMA_PDATAALIGN_BYTE;

hdma_tim1_ch1.Init.MemDataAlignment = DMA_MDATAALIGN_BYTE;

hdma_tim1_ch1.Init.Mode = DMA_NORMAL;

hdma_tim1_ch1.Init.Priority = DMA_PRIORITY_HIGH;

hdma_tim1_ch1.Init.FIFOMode = DMA_FIFOMODE_DISABLE;

//hdma_tim1_ch1.Init.FIFOThreshold = DMA_FIFO_THRESHOLD_1QUARTERFULL;

hdma_tim1_ch1.Init.MemBurst = DMA_MBURST_SINGLE;

hdma_tim1_ch1.Init.PeriphBurst = DMA_PBURST_SINGLE;

if (HAL_DMA_Init(&hdma_tim1_ch1) != HAL_OK)

{

Error_Handler();

}

__HAL_LINKDMA(htim_pwm,hdma[TIM_DMA_ID_CC1],hdma_tim1_ch1);

/* USER CODE BEGIN TIM1_MspInit 1 */

/* USER CODE END TIM1_MspInit 1 */

}

}init TIM1 PWM is running at 1.3MHz

static void MX_TIM1_Init(void)

{

/* USER CODE BEGIN TIM1_Init 0 */

/* USER CODE END TIM1_Init 0 */

TIM_OC_InitTypeDef sConfigOC = {0};

/* USER CODE BEGIN TIM1_Init 1 */

/* USER CODE END TIM1_Init 1 */

htim1.Instance = TIM1;

htim1.Init.Prescaler = 0;

htim1.Init.CounterMode = TIM_COUNTERMODE_UP;

htim1.Init.Period = 0xAA;

htim1.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1;

htim1.Init.RepetitionCounter = 0;

htim1.Init.AutoReloadPreload = TIM_AUTORELOAD_PRELOAD_DISABLE;

if (HAL_TIM_PWM_Init(&htim1) != HAL_OK)

{

Error_Handler();

}

sConfigOC.OCMode = TIM_OCMODE_PWM1;

sConfigOC.Pulse = 0x55;

sConfigOC.OCPolarity = TIM_OCPOLARITY_HIGH;

sConfigOC.OCNPolarity = TIM_OCNPOLARITY_HIGH;

sConfigOC.OCFastMode = TIM_OCFAST_ENABLE;

sConfigOC.OCIdleState = TIM_OCIDLESTATE_RESET;

sConfigOC.OCNIdleState = TIM_OCNIDLESTATE_RESET;

if (HAL_TIM_PWM_ConfigChannel(&htim1, &sConfigOC, TIM_CHANNEL_1) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN TIM1_Init 2 */

/* USER CODE END TIM1_Init 2 */

HAL_TIM_MspPostInit(&htim1);

}static void MX_DMA_Init(void)

{

/* DMA controller clock enable */

__HAL_RCC_DMA2_CLK_ENABLE();

/* DMA interrupt init */

/* DMA2_Stream6_IRQn interrupt configuration */

HAL_NVIC_SetPriority(DMA2_Stream6_IRQn, 0, 0);

HAL_NVIC_EnableIRQ(DMA2_Stream6_IRQn);

}- Labels:

-

STM32H7 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 04:56 AM

Read out and check content of relevant TIM (_DIER), DMAMUX and DMA registers (and peripahs also the GPIOE registers).

Is the source memory DMA-ble (as per caching status)?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-03 07:55 AM

Hi all,

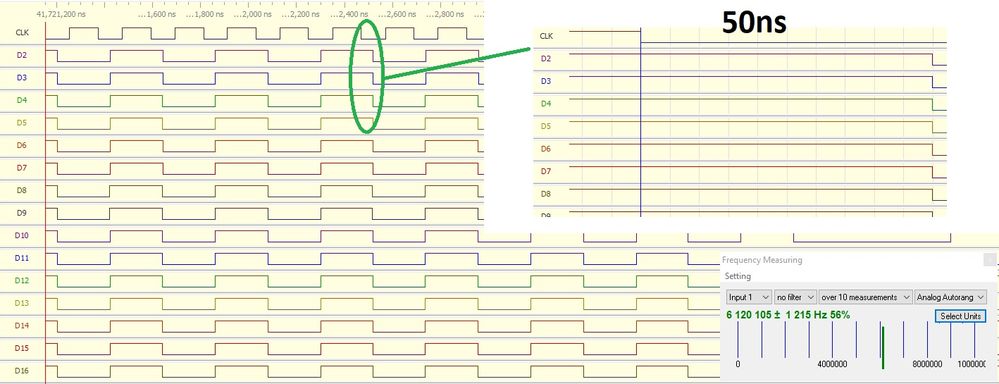

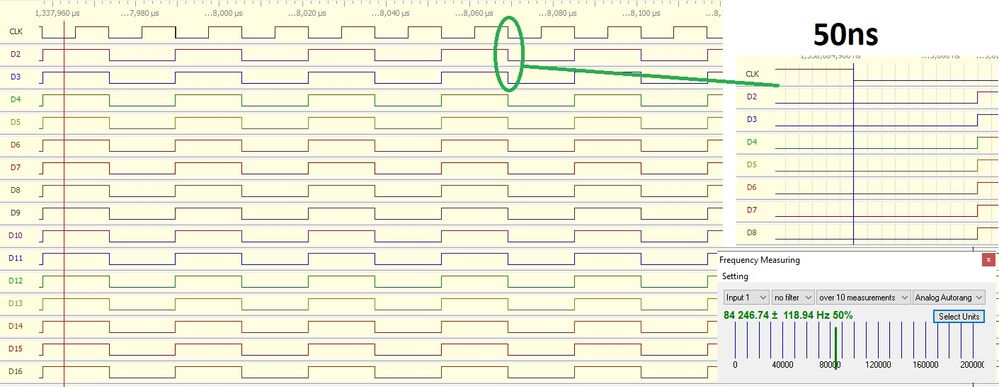

I make it work with BDMA and LPTIM2 and SRAM4, but here is 50ns offset between Clock (LPTIM2 PWM) and 16bit gpio.

As I mentioned before I need parallel synchronous transmission so I would like to eliminate 50ns offset between clock and data.

I trying to make synchronisation at falling edge of CLK. And my goal is reach 16MHz.

It is even possible with STM32H7 ?

Thank you

Regards

mv

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-17 01:09 PM

I'd like to attempt the same thing with the STM32F746 except using an 8 bit parallel interface, could you post your source code?

Thanks,

Doug Burrell

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-30 06:53 AM

See my solution how to do this with BDMA or DMA:

See my STM32H7 forum post "Parallel transmission using GPIO and DMA (like AN4666)"

- STM32H743 SPI with CRC mode, acces to CRC from frame in STM32 MCUs Products

- STM32H743 memory bandwidth issues with DCMI, FMC, ADC, parallel bus, DMA1, DMA2 / DCACHE issue in STM32 MCUs Embedded software

- Trying to operate WL55JC1/L072Z LRWAN1 in Class C in STM32 MCUs Wireless

- The DMA impact of SPI on ETH in STM32H7 in STM32 MCUs Products

- On Nucleo board H743ZI, HAL in use, byte wise TRX setup,after few bytes sent, no TX anymore. in STM32 MCUs Embedded software