- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32G0 ADC clock. Max. asynchronous clock accordi...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G0 ADC clock.

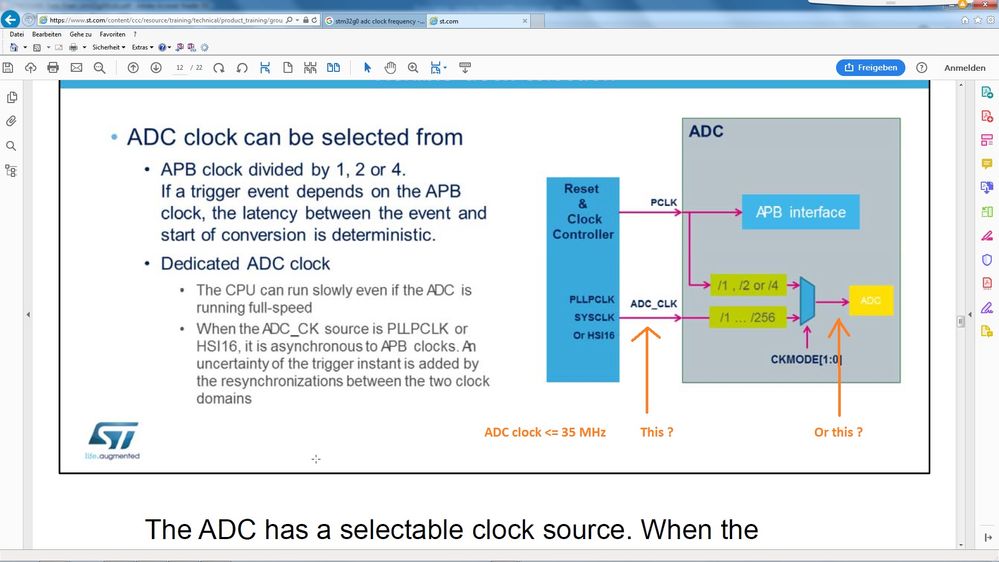

Max. asynchronous clock according to datasheet is 35 MHz.

Is this (35 MHz) the input to PRESC or the output of PRESC ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-21 1:35 AM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-17 11:23 AM - edited 2024-08-17 11:25 AM

Yes, 32 MHz is okay, 64 not.

( The effective clock going to the ADC, after the prescaler. )

And set a sampling time, that's big enough to match the source impedance, see ds about that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-31 7:39 AM

The ACD clock limitation is behind the divider (in your picture marked as "Or this ?")

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-17 9:37 AM

My question is in CubeMx Configuration the PCLK is 64MHz in my case STM32G070RB series and similarly to ADC clk configure at 64MHz.

if i configure ADC setting clock prescalar as synchronous clock mode divide by 2 means -> ADC operate at 32MHz. It is within the range of ADC characteristics mention in datasheet (f_ADC =35MHz (max)) to get optimum performance of ADC.

If i choose ADC clock prescalar as asynchronous clock mode divide by 1 means -> ADC operate at 64MHz. This configuration may cause any adc performance problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-17 11:23 AM - edited 2024-08-17 11:25 AM

Yes, 32 MHz is okay, 64 not.

( The effective clock going to the ADC, after the prescaler. )

And set a sampling time, that's big enough to match the source impedance, see ds about that.

- TCXO Not Supported by SUBGHz_PHY Middleware in STM32CubeMX for STM32WL5MOCHTR in STM32 MCUs Wireless

- STM32F103RBT6 SPI slave mode in STM32 MCUs Products

- One USB port for both ST-Link and user device applications in STM32 MCUs Boards and hardware tools

- USB trace impedance for STM32H725 in STM32 MCUs Products

- NUCLEO-H723ZG BOARD ADC NOISE in STM32 MCUs Products