- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F205 USART2 Long zero level in tx transmi...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F205 USART2 Long zero level in tx transmitting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-17 03:21 AM

I use USART2 for connect whith gsm module.

When trafic is big enough some byte in transmitting from cpu to modem can be corrupted.

It may be happen one time in few minutes.

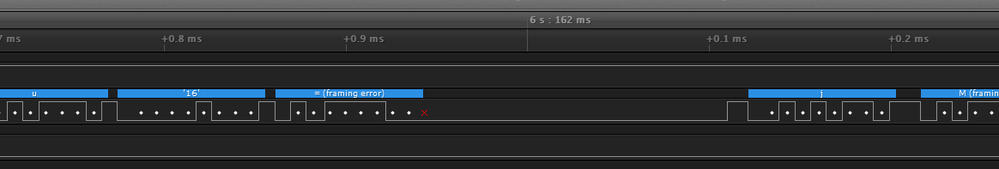

I see corrupted byte by signal analisator. And the same corruption i see on the server side.

Problem has occurred in the middle of the packet (not beginning and ending bytes).

I have used different methods for transmitting - interrupt, interrupt only by tx compit, dma.

All methods have the same result.

I have impression that Usart is switced off, or ahb frequency has changed for some ms.

But i can't imagine in which place of code it can be.

TX pin is setup for output high level, So if Usart is switched off logical one must be on tx.

Boud rate is ok.

I don't understand what can be cause of that behavour. How USART TX pin can be in low level so long time (more than byte duration)

CTS control is used. I have tried hardware and sowtware flow control. Issue is in both cases.

- Labels:

-

RCC

-

STM32F2 Series

-

UART-USART

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-17 05:54 AM

What are you using for the clock source, HSE, HSI? If HSE, do you have CSS enable to detect a clock dropout?

Did you check to make sure you're not sending a BREAK?

Jack Peacock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-17 06:56 AM

I'd say, short to a neighbouring pin/track.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-17 08:37 PM

Hi. Thanks for answers!

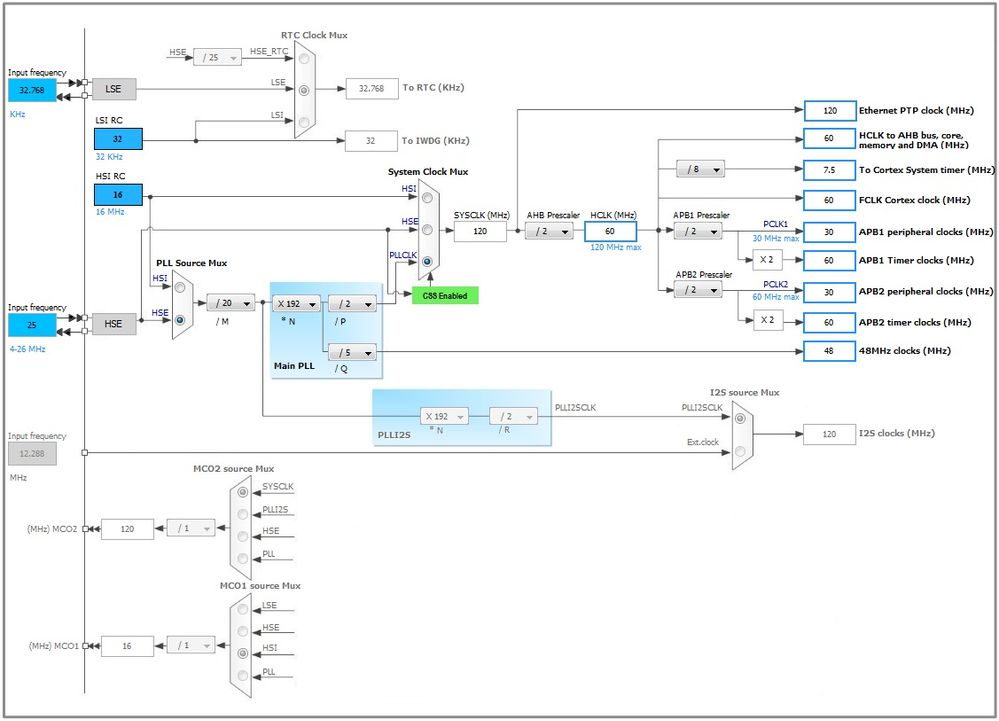

I use HSE and PLL. Clocking sceme is in attach.

clock dropout is a good idea! I didn't suppse that it can be at all. When I switch on CSS usart is failing more faster, and doesn't return in normal mode.

I don't use sending breaks. I am sure. And low levels can be more longer than breaks. Long ones can be too.

I doubt It can be short between neighbouring pins. It occurs on different devices. And different types of devices.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-17 08:51 PM

Yes. NMI is called when CSS is on.

So MCU is acting from HSI in that case and USART works on another speed constantly.

Why could be clock drops? What could be cause?

I suppose when HSI is switched by CSS switching back to HSE doesn't work automatically. Is it true?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-19 04:13 AM

Good day!

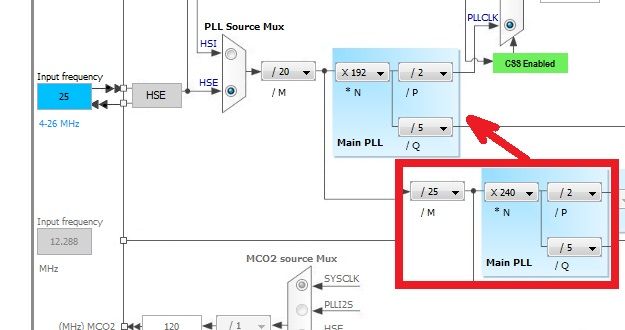

The problem was solved by changing PLL settings.

CSS doesn't detect clock dropouts after that.

But It is strange enough.

CSS detects HSE failings.

We have changed pll settings. Could pll settings have affection on HSE?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-02 03:01 PM

Indirectly, through VDDA.

Review power supply, VDD/VDDA and grounding arrangement.

Review the crystal circuitry, check whether capacitors are adequate to the used crystal. 25MHz is at the upper edge of HSE usability and is quite a high frequency for a crystal, maybe you would want to use a lower frequency crystal for stability.

JW

- MCSDK project enters in TSK_HardwareFaultTask() when I try to use USART2 transmit in STM32 MCUs Motor control

- STM32 Nucleo F303RE: USART1 DMA not receiving data from GY-25 sensor in STM32CubeIDE (MCUs)

- STM32F103C8T6 does not transmit or receive on UART2 in half duplex in STM32 MCUs Embedded software

- How to Transmit Raw Decimal Values (0-255) using UART? in STM32 MCUs Embedded software

- Data transmission and reception using UART in STM32CubeMX (MCUs)