- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeProgrammer (MCUs)

- Re: Did I brick my STM32F2?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Did I brick my STM32F2?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 03:18 PM

Hi all -

I'm modifying some legacy code written for a WICED device that contains an STM32F2xx. The original programmer had a passage that reduces down to:

#define OB_RDP_Level_0 ((uint8_t)0xAA)

#define OB_RDP_Level_1 ((uint8_t)0x55)

FLASH_OB_Unlock();

FLASH_OB_RDPConfig( OB_RDP_Level_1 );

FLASH_OB_Launch();

FLASH_OB_Lock();

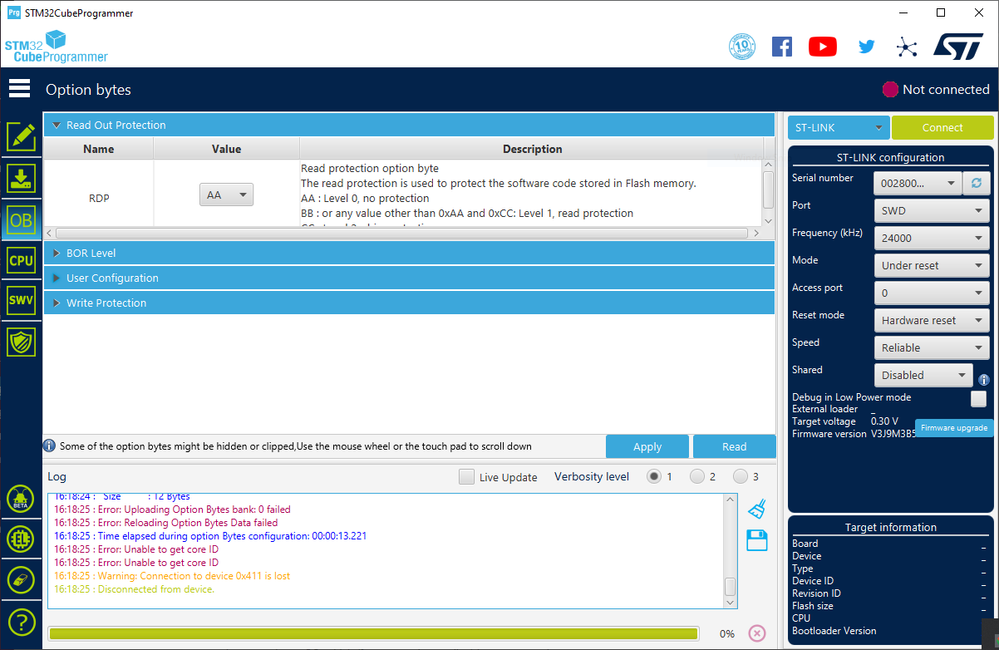

NVIC_SystemReset( );I have no idea where he got the value "55" but the upshot is I can't reset my OBs. When I try, I get this output from the programmer software:

15:15:33 : Option byte command : -ob RDP=170

15:15:33 : PROGRAMMING OPTION BYTES AREA ...

15:15:33 : Bank : 0x00

15:15:33 : Address : 0x40023c14

15:15:33 : Size : 12 Bytes

15:15:52 : UPLOADING OPTION BYTES DATA ...

15:15:52 : Bank : 0x00

15:15:52 : Address : 0x40023c14

15:15:52 : Size : 12 Bytes

15:15:52 : Error: Uploading Option Bytes bank: 0 failed

15:15:52 : Error: Reloading Option Bytes Data failed

15:15:52 : Time elapsed during option Bytes configuration: 00:00:18.761

15:15:52 : Error: Unable to get core ID

15:15:52 : Error: Unable to get core ID

15:15:52 : Warning: Connection to device 0x411 is lost

15:15:52 : Disconnected from device.So, my questions are:

- does anyone know what a value of "55" will do in this situation? (I guess what I'm really asking is, is it possible that it got interpreted as "CC"?)

- Any suggestions for un-bricking this? I've unplugged and disconnected everything a few times.

Thanks for any assistance...

- Labels:

-

Flash

-

RAM

-

STM32CubeProgrammer

-

STM32F2 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 04:05 PM

1) What exactly is not clear from the description in reference manual?

0xAA: Level 0, no protection

0xCC: Level 2, chip protection (debug and boot from RAM features disabled)

Others: Level 1, read protection of memories (debug features limited)

2) Probably try SWD interface with a "connect under reset".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 04:15 PM

These are the settings I've used...thanks.

- STM32G071CBU6 DFU and UART Bricking issue in STM32CubeProgrammer (MCUs)

- Macro for different DMA types in STM32CubeIDE (MCUs)

- [STM32G051] Totally Brick after incorrect option byte change behavior. in STM32CubeProgrammer (MCUs)

- No STM32 target found in STM32CubeProgrammer (MCUs)

- Writing to flash bricks stm32G030 and stm32G031 in STM32CubeIDE (MCUs)