- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Cortex system timer config bug?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Cortex system timer config bug?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-26 03:57 PM

According to RM0456, section 11.4 RCC clock functional description, p. 482:

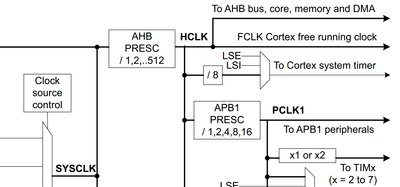

"The RCC feeds the Cortex system timer (SysTick) external clock with the AHB clock (HCLK) divided by eight, or LSE or LSI. The SysTick can work either with this clock or directly with the Cortex clock (HCLK), configurable in the SysTick control and status register."

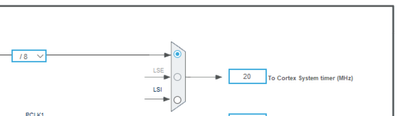

However, the corresponding clock settings, at least for STM32U5A5 seem to make no impact. Regardless of what is set, the generated source code is exactly the same.

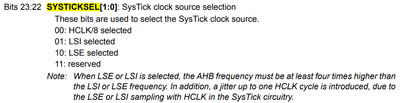

The SysTick source is controlled by RCC_CCIPR1.SYSTICKSEL register

Figure 36. Clock tree for STM32U5 Series

RM0456 does not clearly explain where the related STCALIB register mentioned in section 22.2 is located and how to set SysTick to work directly with HCLK. RCC_CCIPR1.SYSTICKSEL register (section 11.8.46) allows only for three values:

00: HCLK/8 selected,

01: LSI selected,

10: LSE selected

I am puzzled. Probably those who tried to implement this CubeMX config function were unclear as well.

Please advise.

- Labels:

-

RCC

-

STM32CubeMX

-

STM32U5 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-26 04:12 PM - edited 2024-02-26 04:19 PM

IIRC this was a bug in the CubeMX/IDE for earlier products. The /8 divisor was not taken into account. Looks that the systick selector mux is still not implemented in Cube for U5?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-26 04:57 PM

HCLK would come from the selection in the SYSTICK peripheral itself, not ST's circuit

SYST_CSR.CLKSOURCE

CubeMX probably has some separate configuration of SysTick itself.

Sure it's unhelpful from a point-and-click point of view, but that comes with the territory

Up vote any posts that you find helpful, it shows what's working..

- Viewing SWO without STM32CubeIDE in STM32CubeIDE (MCUs)

- STM32F429 / STM32G491 What is the difference in external loader? in STM32CubeProgrammer (MCUs)

- Trouble Setting Up STM32 Development with VS Code on Zorin OS in STM32 VSCode extension (MCUs)

- STM32CubeProgrammer Failure on STM32L4 with Error: Operation exceeds memory limits in STM32CubeProgrammer (MCUs)

- Building STM32CubeMX generated project using make (msys2) on Windows 11 in STM32CubeMX (MCUs)