While using STM32L476 ADC to monitor a signal, the data showed a severe distortion. Has anyone comed up with such a problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-26 8:02 PM

I made a board with STM32L476RG chip to pick up a little signal with ADC module, but ended up with a severe distortion.

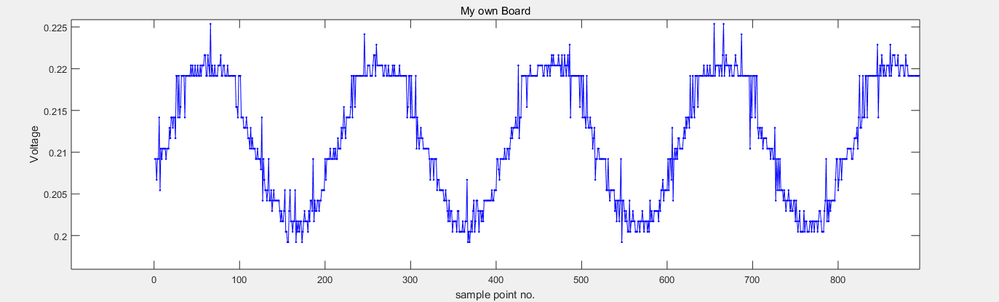

Then I tested the board with sine signal of 20mVpp, 300mVbias. The signal is generated by a signal generator. The result can be seen in the following picture. Known that the sampling resulotion is 12-bit, which means that with 3.3V VREF, the actual resulotion is 0.8mV. So the stages shown here is not caused by the sampling precision.

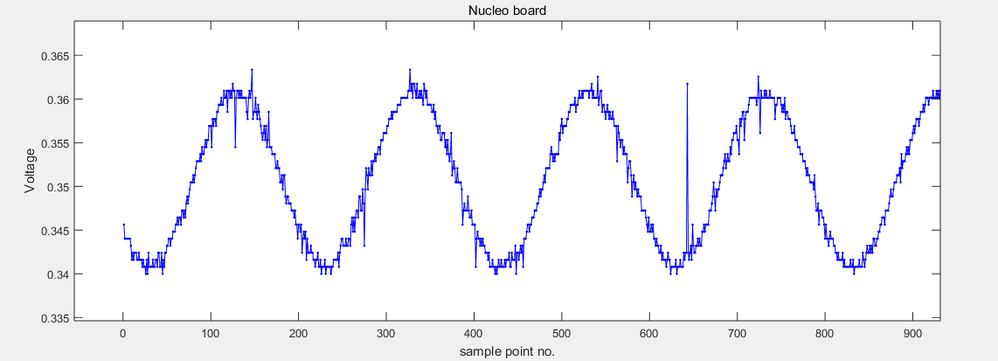

For comparation, I tested the STM32L476RG nucleo board with the same code and same signal, and the result is as below. The signal picked by nucleo board is apparently different with the signal above. Although the stages are still there, but it is resonable and the sine wave is correct. And another point is that the bias tested by the nucleo board is higher than my own board, while the input is the same.

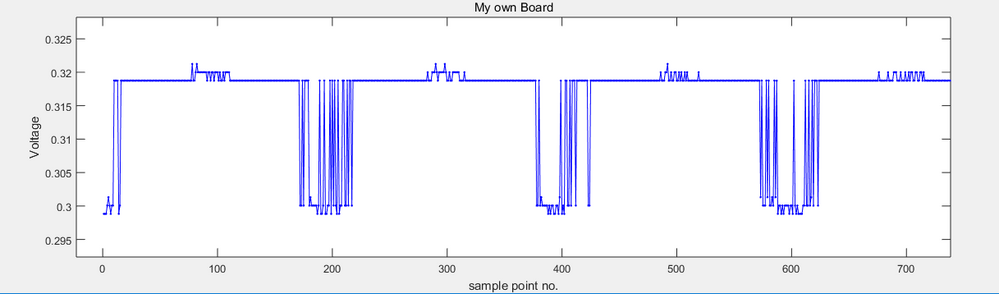

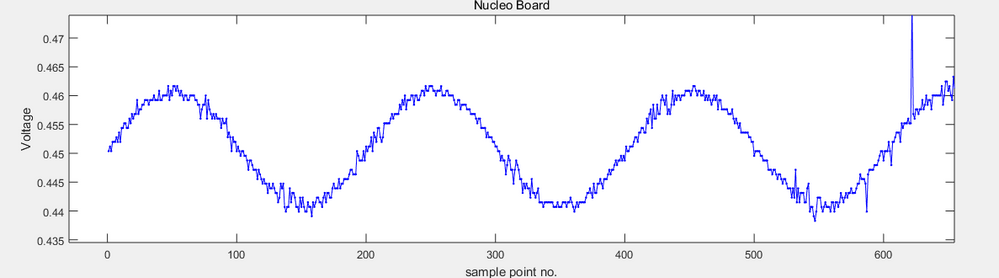

Further more, if i give a higher bias to the input signal, the distrotion will change. There are two pictures below, which shows the data picked by my board and nucleo board.

This is the discription of the problem I comed up with. Has anyone comed up with similar problems? What can the reason be?

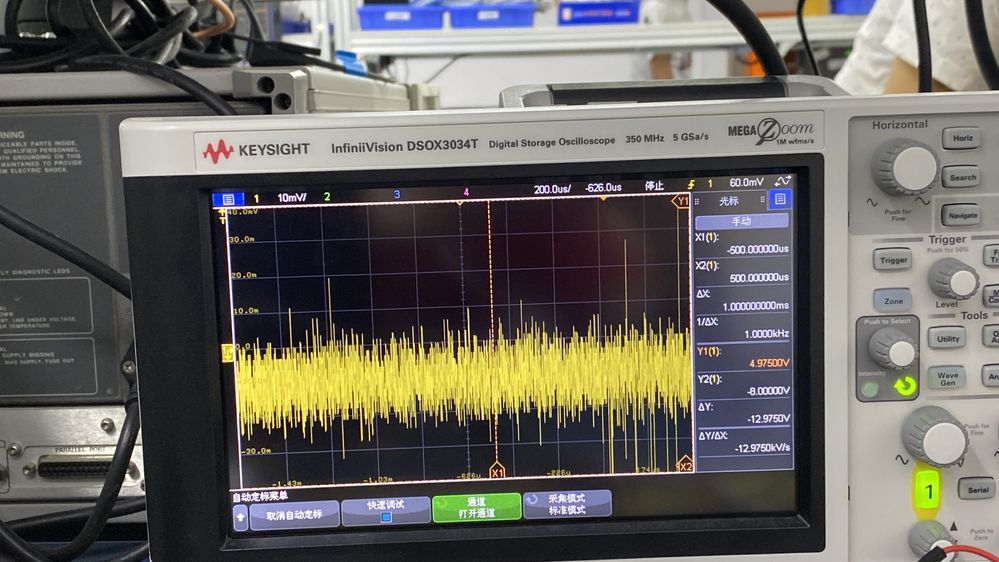

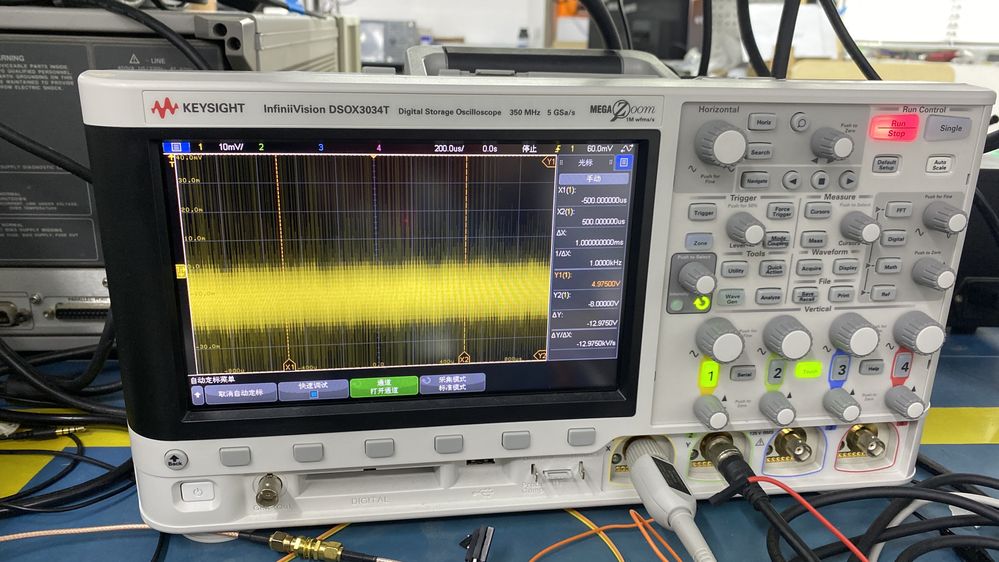

I thought that one of the reason can be the referance voltage. Since STM32L476RG is a 64-pin chip, the VREF of ADC is directly connected to Vdd and Vss, so I ovserved the voltage between Vdd and Vss with a oscilloscope, the result is as below.

At the same time , I observed the Vss of nucleo board, the result is similar, and is put below. The time-axis scale is a little different, but the result I observed showed no difference.

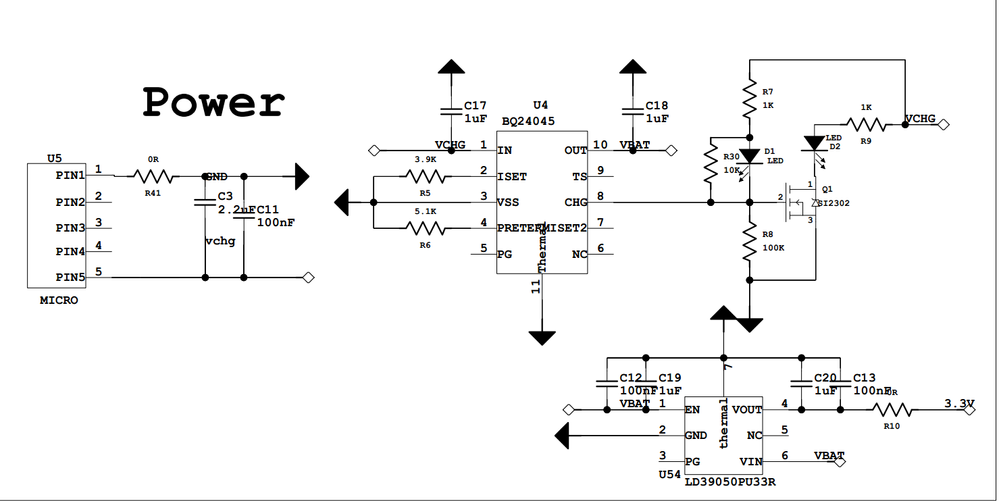

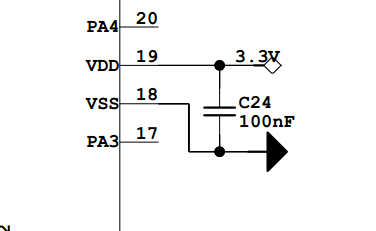

By the way, the design of the power part is also here. And the 3.3V network is connected directly to the VDD and VSS pin.

--------------------------------------------------------------------------------------------------------------------------------

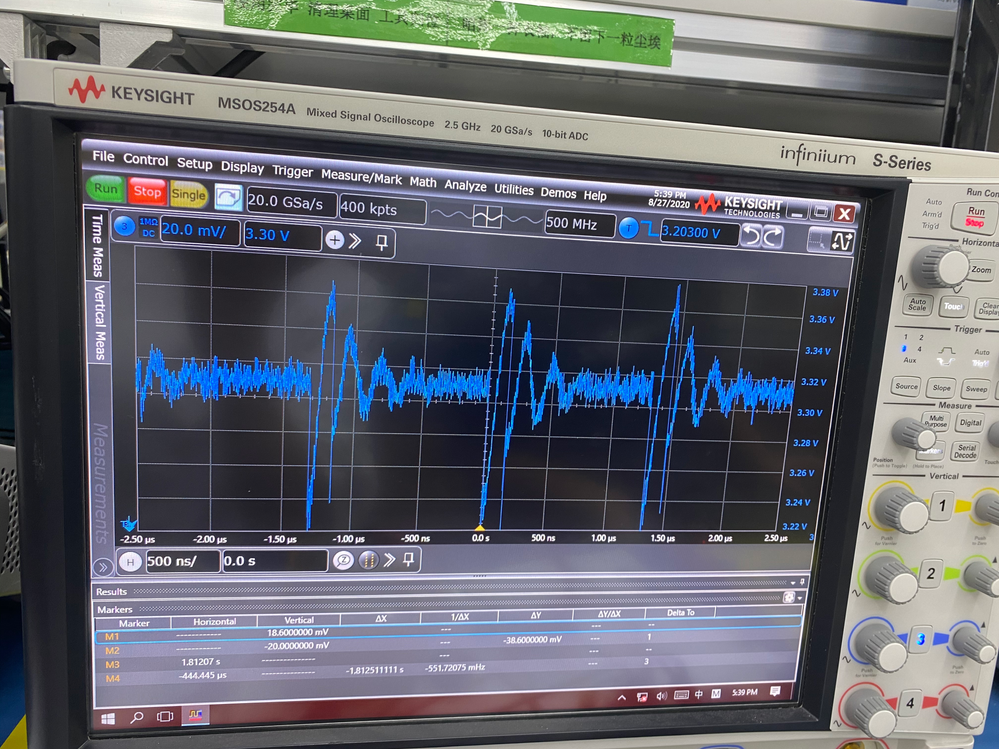

Ok everyone, I think I found the problem. I ovserved the voltage of VDDA pin, which is connected to Vref, and catched a large wave. The amplifile of the wave is over 60mVpp。

While the official nucleo board did't have such a wave.

I solved the problem. Because my colleague told me that the bead used on VDDA has a 2Ω resistance. So I changed it to a 0Ω, and the distortion disappeared.

A lot of thanks to everyone!

Solved! Go to Solution.

- Labels:

-

ADC

-

STM32L4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-27 2:16 AM

I updated my observation above and I think I have found the reason.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-26 9:13 PM

The first two plots don't look the same. Both are 0.02Vpp, but the second has higher resolution.

If your input signal is high-impedance, you can get odd behavior like this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-26 11:06 PM

Actually, the resolution of the 2 boards are all 12-bit, so it is really strange.

I tried both 50Ω and Hiz impedance of the input signal, but turned out that this odd behavior didn't change.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-26 11:43 PM

> VREF of ADC is directly connected to Vdd and Vss

Not VDD but VDDA.

Check directly on the VDDA pin of mcu. Check *all* ground pins (I am assuming at bad solder joints). Check for ground loops, try some other signal side than the signal generator (e.g. a soundcard).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-27 12:17 AM

Thank you for the suggestions, I will check the pins. And I will try different signal source. I will update my results in the discription of the question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-27 2:16 AM

I updated my observation above and I think I have found the reason.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-07 4:44 AM

Thanks @SLei.1 for sharing your findings.

For those who missed the soljtion on your original post: : "I solved the problem. Because my colleague told me that the bead used on VDDA has a 2Ω resistance. So I changed it to a 0Ω, and the distortion disappeared."

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.