- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F412 SPI DMA data bit-shifted

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F412 SPI DMA data bit-shifted

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-29 04:15 PM

Hi.

First of all, the essence of my problem is already described here - https://community.st.com/s/question/0D50X00009XkiXu/spi-dma-data-corruption?t=1567119350874

In my case bug happens randomly and not very often. It could be one corrupted transaction among hundreds-thousands.

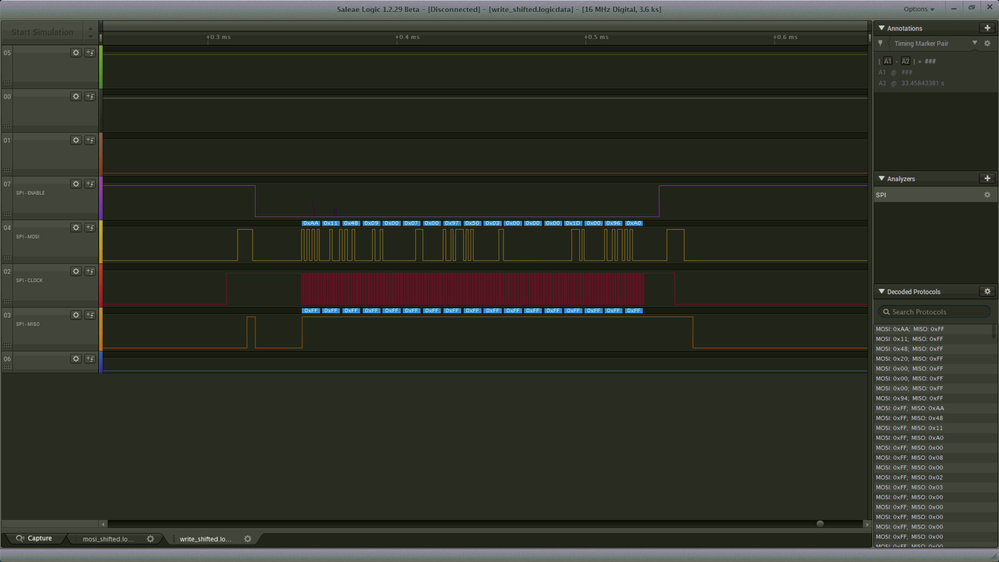

For example, how it is should work:

First byte always is 0xAA.

Here is an example of corruption:

You can see that CLK signal has already started, but data on MOSI is delayed by 5 bits (not constant, can be 4, 3...).

My code: https://pastebin.com/X3CfdH4q

And settings: https://pastebin.com/GKWTC1QH

- Labels:

-

DMA

-

SPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-09 09:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-09 09:32 AM

Sorry I don't have the Saleae analyzer and don't intend to install the program. Can you please cut out the "previous" and "corrupt" transfer and place them next to each other?

[EDIT] Okay maybe it's not that necessary. Try to answer the following question first, and then perhaps mitigate it - if the signals are floating, try to set pullups/pulldowns as appropriate, especially to SCK [/EDIT]

Also, what is the SPI_ENABLE signal? And why are the SPI signals changing after the transfer ended?

Thanks,

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-09 09:53 AM

SPI_ENABLE is slave select line.

After end of the transfer I execute disable and deinit SPI (including clock disable - RCC_APB2PeriphClockCmd) and change MISO/MOSI/SCK pins to INput mode with pull-down.

You can see similar state-changing on start of the transfers too.

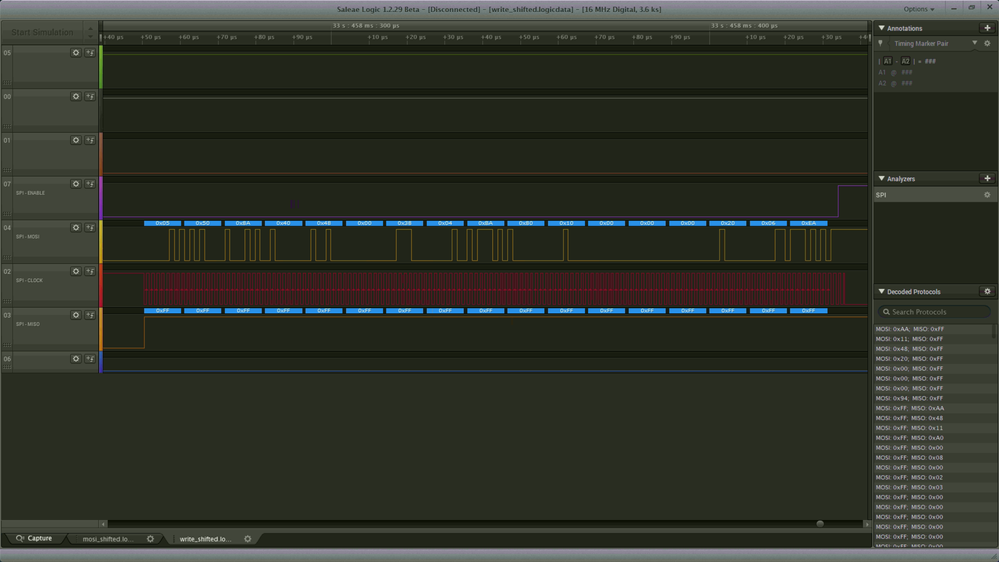

Combined previous--->corrupted transfers:

"Previous" closer view:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-09 11:07 PM

> After end of the transfer I execute disable and deinit SPI (including clock disable - RCC_APB2PeriphClockCmd) and change MISO/MOSI/SCK pins to INput mode with pull-down.

Okay, so don't do this. Leave the SPI on. And, as as you CPOL so that SCK is high on idle, don't use an pulldown, us a pullup to avoid any transition on SCK.

I'd say, the exact sequence how you re-enable the SPI includes a period, where the SPI is slave and its clock is floating, resulting in the internal clock-counter to be shifted out of 0 and remaining so even if switched to master. The bunch of pulses on MISO in the "corrupted transfer" at the moment when the _ENABLE signal goes low is IMO not a coincidence.

The SPI state machine is relatively fragile. SPI_CR1.SPE is always the last bit to be set.

I don't Cube.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-12 06:22 AM

Thank you for your advice, I'll try with corrected init sequence.

By the way - I have disabled DMA and still got the same error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-12 06:29 AM

> By the way - I have disabled DMA and still got the same error.

I'd expect that, the problem appears to be entirely in the SPI and the way how it counts bits.

JW

- « Previous

-

- 1

- 2

- Next »

- Problem on replacing MCU in STM32CubeIDE (MCUs)

- STM32F412 CAN Transmits unexpected data in STM32 MCUs Products

- STM32F412 I2C2 Busy flag keeps set in STM32 MCUs Products

- STM32CubeProgrammer 2.16 - cannot program MCU by USB in STM32CubeProgrammer (MCUs)

- EXTI0 double interrupt on one edge in STM32 MCUs Products