- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F3 - what is ITR2 for TIM3?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F3 - what is ITR2 for TIM3?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 4:36 AM

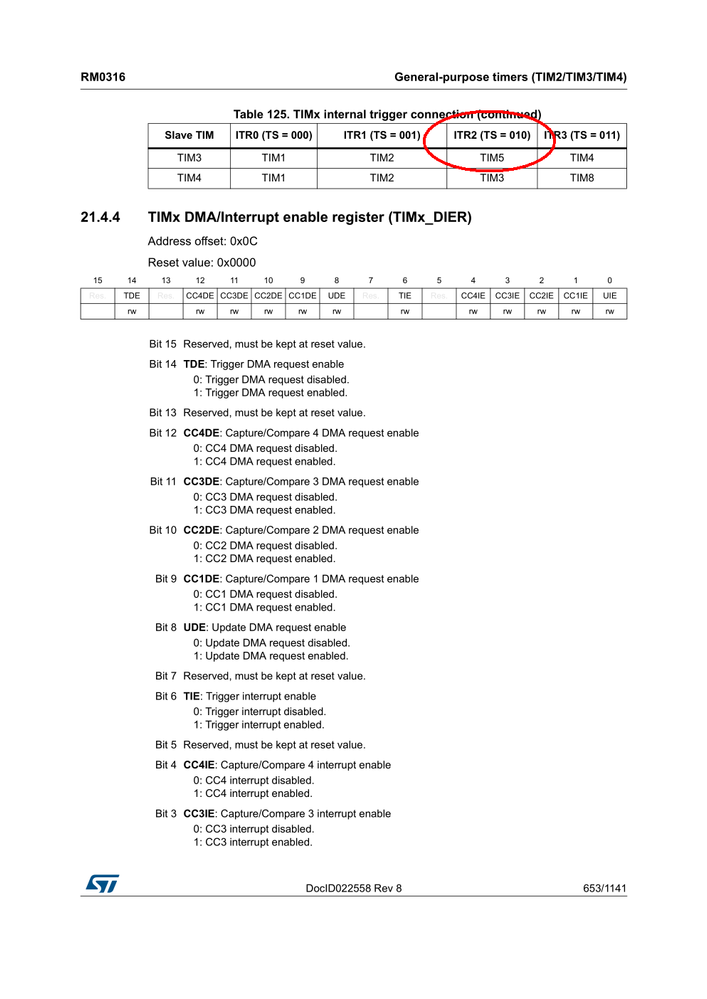

RM0316 says it's TIM5:

but there's no TIM5 in the 'F3 (except 'F373, to which RM0316 does not apply).

ST please clarify.

JW

PS. Textual search finds TIM5 also in description of the TIMx_CCRx registers, obviously copy-paste relics.

Solved! Go to Solution.

- Labels:

-

Documentation

-

STM32F3 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 11:35 AM

Confirming TIM15 to be ITR2 for TIM3 in STM32F303RB.

#define TIM_CR2_MMS__UPDATE 2 // update event -> TRGO

#define TIM_SMCR_SMS__EXT_CLK_1 7

#define TIM3_SMCR_TS__TIM15 2

RCC->APB1ENR |= 0

OR RCC_APB1ENR_TIM3EN

;

RCC->APB2ENR |= 0

OR RCC_APB2ENR_TIM15EN

;

TIM15->ARR = 1000 - 1;

TIM15->CR2 = 0

OR (TIM_CR2_MMS__UPDATE * TIM_CR2_MMS_0) // set update event as TRGO

;

TIM15->CR1 = 0

OR ( 1 * TIM_CR1_CEN ) /* Counter enable */

;

//

TIM3->SMCR = 0

OR (TIM3_SMCR_TS__TIM15 * TIM_SMCR_TS_0 )

OR (TIM_SMCR_SMS__EXT_CLK_1 * TIM_SMCR_SMS_0 ) // external clock mode 1

;

TIM3->CR1 = 0

OR ( 1 * TIM_CR1_CEN ) /* Counter enable */

;results in TIM3_CNT running.

Still would like to see this being fixed in both the RM, and AN4651. @Imen DAHMEN can you please have a look at this? Thanks.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 6:16 AM

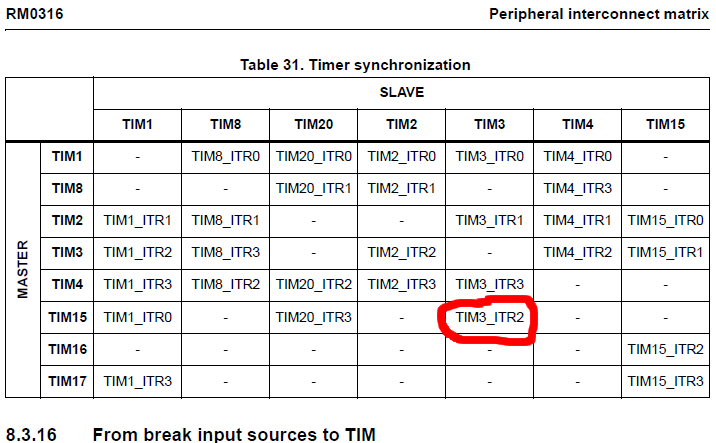

Looks like a typo, it should be TIM15

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 6:58 AM

Thanks, Peter, I've seen it, and will test it; but would like ST to comment nevertheless.

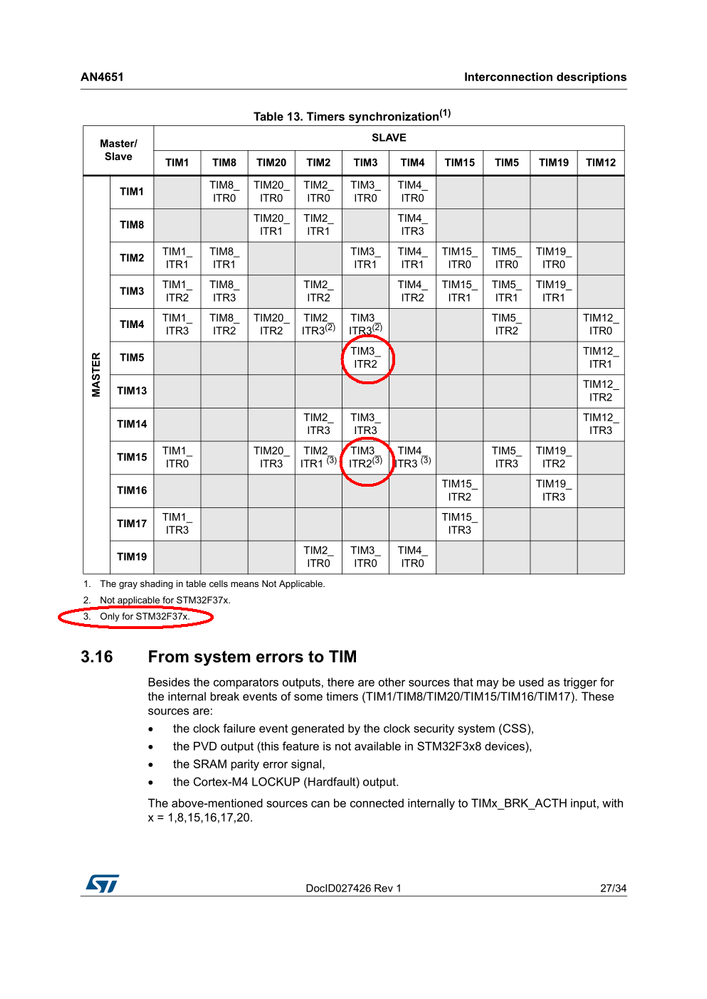

Meantime, more of this in the dedicated 'F3 "interconnections" appnote:

That whole table is of course a disaster - the 'F373 matrix is quite different and should've been taken out to a different table.

The tables in RM0316 should also account - at least in a footnote - for the unavailability of certain timers in certain models, e.g. TIM20 is available only in 'F303xD/E, TIM4 and TIM8 are not available

in 'F303x6/8 etc.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 7:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 11:35 AM

Confirming TIM15 to be ITR2 for TIM3 in STM32F303RB.

#define TIM_CR2_MMS__UPDATE 2 // update event -> TRGO

#define TIM_SMCR_SMS__EXT_CLK_1 7

#define TIM3_SMCR_TS__TIM15 2

RCC->APB1ENR |= 0

OR RCC_APB1ENR_TIM3EN

;

RCC->APB2ENR |= 0

OR RCC_APB2ENR_TIM15EN

;

TIM15->ARR = 1000 - 1;

TIM15->CR2 = 0

OR (TIM_CR2_MMS__UPDATE * TIM_CR2_MMS_0) // set update event as TRGO

;

TIM15->CR1 = 0

OR ( 1 * TIM_CR1_CEN ) /* Counter enable */

;

//

TIM3->SMCR = 0

OR (TIM3_SMCR_TS__TIM15 * TIM_SMCR_TS_0 )

OR (TIM_SMCR_SMS__EXT_CLK_1 * TIM_SMCR_SMS_0 ) // external clock mode 1

;

TIM3->CR1 = 0

OR ( 1 * TIM_CR1_CEN ) /* Counter enable */

;results in TIM3_CNT running.

Still would like to see this being fixed in both the RM, and AN4651. @Imen DAHMEN can you please have a look at this? Thanks.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-22 1:31 AM

Hello,

Thank you for highlighting this issue. I will check and raise this internally to fix all impacted documentations.

Note that the correction is already integrated in the next release of RM0351 (Rev 7) as reported in this discussion: https://community.st.com/s/question/0D50X00009sWbv9SAC/masterslave-problem-on-tim3-in-stm32l476-slave-not-counting-when-itr2-selected.

Best Regards,

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-22 3:04 AM

Thanks, Imen.

Please note that this time it's the 'F3 (thus RM0316) not 'L4; I just mentioned the 'L4 thread because it's quite strangely the same error even if it is a completely different family.

Jan

- PWM Out follow PWM in(Capture) as same as Duty cycle and Frequence(Synchronize) in STM32 MCUs Products

- Stm32G030 Timer : problem by using TIM17 OC1 as internal trigger for TIM1 in STM32 MCUs Products

- configure master/slaves timers on stm32f746 in STM32 MCUs Products

- BUG in RM0394 Rev 4, regarding timer (TIM2) synchronization. in STM32 MCUs Products