- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32 SPI with CC1125 (TI)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 SPI with CC1125 (TI)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 04:14 AM

The CC1125 is a TI sub-GHz transceiver: https://www.ti.com/product/CC1125

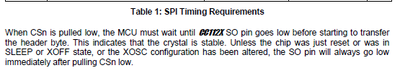

The User's Guide - https://www.ti.com/lit/pdf/swru295 - says that, after asserting CS, the SPI Master must wait for the CC1125 to pull MISO low before starting the transfer:

I think this means that the STM32F0's hardware SPI can't be used?

Unless anyone else can see a way ... ?

- Labels:

-

SPI

-

STM32F0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 04:21 AM

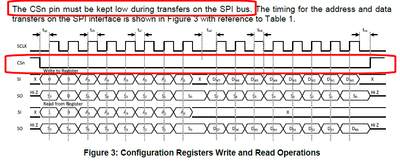

The CC1125 requires that CS remains asserted through the entire communication:

the CC1125 doesn't use the "TI protocol" described in the STM32F0 documentation:

(and that doesn't seem to cover waiting for MISO low anyhow)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 06:12 AM - edited 2023-08-25 06:13 AM

Sounds like you would need to implement the CS pin and waiting logic itself, but could otherwise use it just fine.

- set CS low

- wait for MISO low

- call HAL_SPI_Transmit... or whatever

- set CS high

Waiting doesn't have to be a blocking operation although it would make the program logic a lot simpler.

The IDR register of the MISO pin is still connected/accurate in AF mode, so there's no issue reading it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 10:08 AM

Yes, of course that works - why didn't I think of that in the first place! <facepalm>

Now I have it working between an STM32F0-Disco and a CC1125 dev board.

But not working on the actual custom target board: the initial MISO sync works, but only zeros are ever read back. :frowning_face:

Anyone here with experience of STM32 + CC1125 can think of any gotchas! ?

(I've done it before with an AVR, and think I've got everything covered, but...)

- STM32H7R/S3x: using external QSPI as primary FLASH in STM32 MCUs Products

- Error Occurred While Regenerating Project in STM32CubeMX 6.13.0 in STM32CubeMX (MCUs)

- L072Z LRWAN1: Switch from Class C to A in STM32 MCUs Wireless

- Patching STM32 FW package before build in STM32CubeIDE (MCUs)

- C++ setup in VS code for STM32 in STM32 VSCode extension (MCUs)