- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: SPI non-DMA max speed ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI non-DMA max speed ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 05:29 AM

I am communicating with a TFT LCD and trying to speed things a little bit. At the moment I dont have DMA library written, so I am using standard SPI mode.

I configured the SPI clock as 5Mhz on STM32F407 mcu.

My main clock is PLL on 96Mhz. With APB2 = 2 and APB1 = 4.

Not sure if relevant, but Flash latency is 6 CPU cycles.

Gpio port output speed on CLK,MISO,MOSI is set to Highspeed. (no difference with low speed).

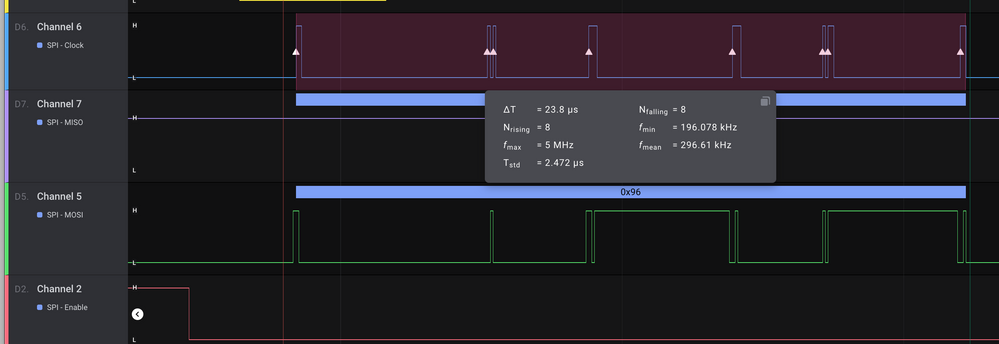

What I am seeing on the logic analyzer is the gaps between each SPI clock. Measuring one byte transmission speed, I am getting average of 300ish Khz instead of 5Mhz.

I only have one interrupt running in the code and that is Systick with 100us tick.

EDIT: One thing was definitely wrong in my setup. CPU WS latency. As my PLL clock is set to 96mhz and mcu works on 3.3v, I had to set 4CPU cycles WS instead of 6 that I originally had. Problem still persists.

- Labels:

-

SPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 05:51 AM

SPI non DMA and DMA have same speed, diff is only offload of mcu when DMA is used.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 06:36 AM

This forum should force users to specify at least an STM32 family prior to post something related.

There are more than 3 generations of SPI IPs from STM32F103 to STM32H7...

One of them allow 32 bit fifo so it means if you don't use interrupt, you could actually send a burst without clock stretch of your data.

If you run SYSCLK at 96MHz, you could run the SPI at 12 Mhz or higher..

SPI is one of the highest bitrate non differential CMOS level serial interface. It's a true candidate for DMA to offload the core.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 06:38 AM

At SPI 12 MHz, 1 bit period is 8 core clocks. If you send 8 bits one shot, it's 64 clocks.

An interrupt usually takes 20+ cycles. There is no SW involvement when the HW is sending the 8 SCK clock pulses to push a byte in and out...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 06:43 AM

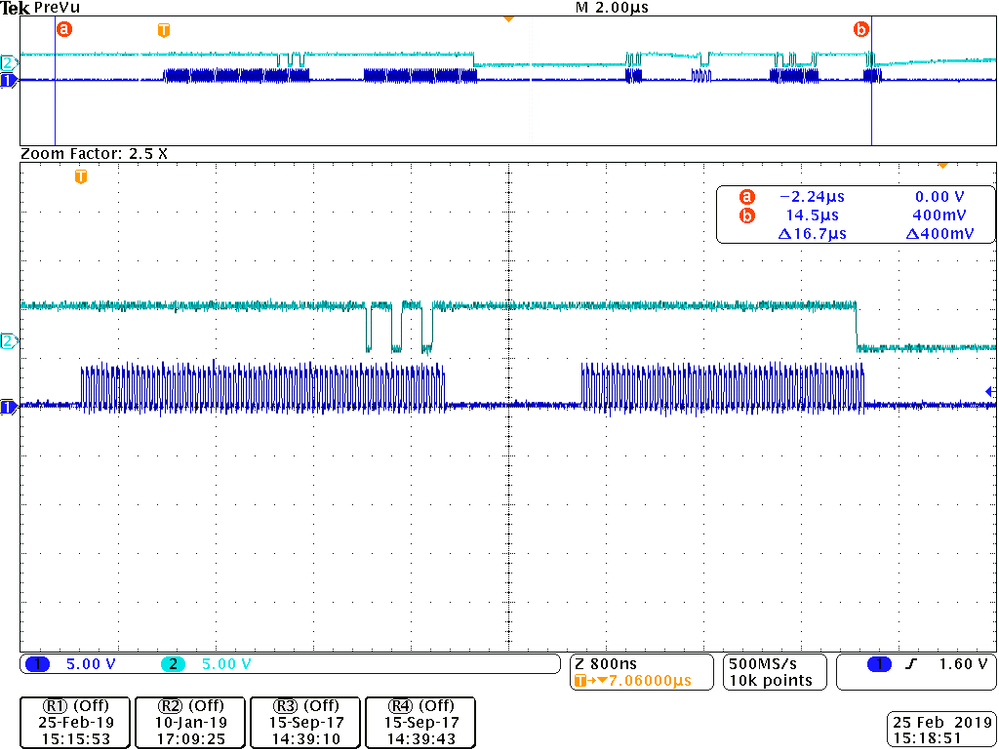

Here is an example of SWD emulation by SPI using non DMA implementation with dynamic SPI bit length adjustments ("3 wire bidir SPI mode")

SYSCLK 48MHz, STM32L4R5

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 06:48 AM

sorry, I added tag for STM32F4.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 07:00 AM

So what could cause the clock to chop like its showed in the attached image? I only showed one character (8bits of data). with inconsistent timing between clock cycles. I would expect burst of 8 SCK clock cycles, and then whatever time in between two characters ..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 07:34 AM

> So what could cause the clock to chop like its showed in the attached image?

MM.1 told you above: slow software.

As a test, write a minimal program which only transmits some random data through SPI. Avoid Cube/HAL or any other "library".

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 08:19 AM

I am not using cube/hal libraries. I am still puzzled on how would any library influence burst of the bits, in my case 8bits on SPI DR register. I could understand delay between 2 bytes of data. This is delay between individual bits of 1 byte of data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-31 09:42 AM

> This is delay between individual bits of 1 byte of data.

Ah, sorry then.

So, you program is already a minimal one, which only transmits a single byte and then just loops indefinitely? If not, write such.

Try it with the default (reset) clock settings. If OK, gradually add features of clock. What's the primary clock source?

Is this a "known good" board like Nucleo/Disco? If no, try the same code on one of those.

Try different pins of the same peripheral, and/or a different incarnation of the peripheral.

Read out and check/post the SPI and GPIO registers' content.

JW

- STM32G473 QSPI indirect read times out at higher frequencies in STM32 MCUs Products

- Motor Driver in STM32 MCUs Motor control

- My board can no longer run the program I uploaded to it earlier in STM32CubeIDE (MCUs)

- Motor Driver in STM32 MCUs Products

- Incremental Encoder Alignment Problem in STM32 MCUs Motor control