- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Interupt responstime issue stm32f429 vs stm32f...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Interupt responstime issue stm32f429 vs stm32f767

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 5:36 AM

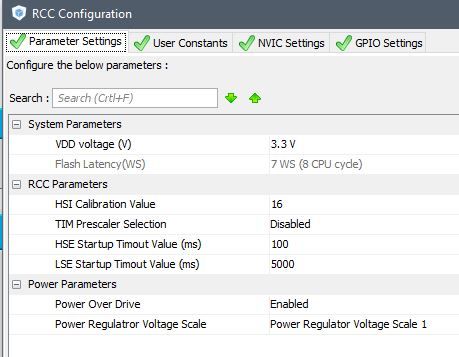

hello,

I'am use for a project the stm32f429. The interrupt handler must react so soon as possible.The stm32f429 interrupt responstime is 218ns.It's fast but not fast enough. I decided to make a new design with the stm32f767 running at 216 mhz. With the same configuration as the stm32f429 running at 180mhzThis configruation is generated with STM32CubeMX / KEIL vision MDK-ARM V5However the interrupt response time is much longer, it is 376ns !!

Well is the processing of instructions faster.What is the reason that the stm32f767 has a longer response time compared to the stm32f429 ??

#interupt-stm32f767-vs-stm32f429-responstime- Labels:

-

Interrupt

-

STM32F4 Series

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 5:58 AM

Instead of trying to explain the many sources of interrupt latency (and there are many of them, most of them hard to control or avoid) and its jitter, and difference between mcu models and other particularities of design, I suggest to give up the idea of having latencies below dozens of machine cycles in any 32-bitter up front.

For controlled latencies below 1us, use hardware. There's plenty of hardware in these chips. Tell us more details of your requirements to receive more help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 7:04 AM

Hi Hans,

Are you measuring the interrupt response time on the first iteration? Could you give as the response times for the second and the third iterations?

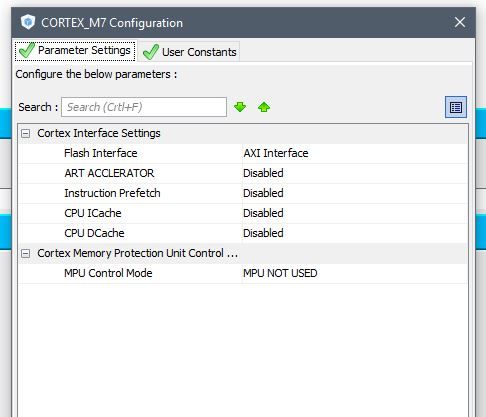

If you will use the STM32F7, I advise you to use the ITCM RAM memory. It is reserved for the CPU Execution/Instruction

useful for critical real-time routines.By the way, what is the the response time value needed for your application ?Note:

Thestm32f429 and

stm32f767 devices do not share the same bus-matrix architecture; So, using the same configuration (with the same clock value) does not mean that you will get the same interrupt time response.

Regards,

Lawliet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 7:19 AM

Hello waclawek.jan thanks for your reply

I am aware that there is faster hardware. Often, there is provided a FPGA with embedded ARM core.

I want to find the limit. The STM comes at the place of a RAM chip, any read / write comes within an interrupt in the STMit works good with the stm32f4 <250ns, the more time I have on the more opportunities I get to influence the RAM data.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 7:42 AM

Some of the possible sources of latency:

- stack in slow memory

- execution from slow memory

- complete vs. lazy FP stacking

Perceived latency (e.g. delay between interrupt edge on input pin and edge on an output pin manipulated at the beginning of ISR) is added up from the hardware latency and any software the compiler might insert between ISR entry and the instruction which performs the pin manipulation. Study the disassembly.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 8:49 AM

Hello Lawliet

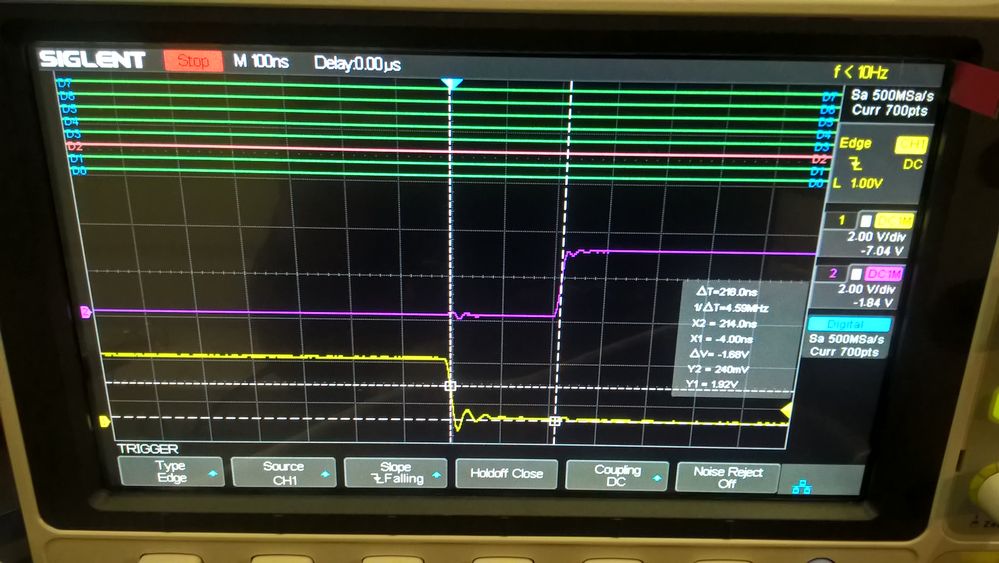

The same configuration I mean the test, see scoop image.

Yellow channel is the chip select connected to the PC0 of the STMThe PCO is configured as ''Interrupt Mode Ecternal widh trigger Falling edge detection''Purple channel is the PG13 standard GPIO output (High speed) GPIOG-> = BSRR GPIO_PIN_13.;Very simlpe test.The question remains, What is the reason the stm32f767 That Has A higher response time Compared to the stm32f429 ??and has the stm32h7 same response time (next year)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 8:56 AM

I gave you several possible reasons above. It's up to you to sort out.

Lawliet gave you

a question

a couple of questions, please answer them (one of them is aimed at the slow memory to execute from, accelerated by cache).JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 9:04 AM

An MCU and an FPGA have different merits... which was commented already.

Assuming this is highest priority level interrupt, and someone would like to reduce the latency, here would be the things to look at:

1. Make the interrupt vectors in RAM

2. Put the interrupt routine in RAM or in CCM memory on F4 (no stolen cycles by DMA)

Let us know how much of a difference this makes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 9:20 AM

I thought The interrupt routine sevice from the STM is running in Flash Memory. is the ''accelerated by cache'' this what you see in the picture ??

I am a beginer ...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-14 9:21 AM

- I have to do the porting from a MCU STM32F429 to a MCU STM32F767.. How do you see the effort in doing the porting? Which are the tricky parts I should consider.. ? The project was designed with sw4stm32 in STM32CubeIDE (MCUs)

- DFUse does not detect my STM32 devices in STM32CubeProgrammer (MCUs)

- STM32F767 Execution time is more compared with STM32F429 in STM32 MCUs Embedded software

- Performance hit running code on STM32F7 vs SMT32F4 in STM32 MCUs Products

- STM32f429 vs STM32F767, process speed? in STM32 MCUs Products