- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: HSI/2 before PLLSRC in STM32F030xC ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

HSI/2 before PLLSRC in STM32F030xC ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-26 9:50 AM

Hi,

I have a problem with the PLLSRC of a STM32F030RC : to obtain 24MHz for the sysclk I have to use PLLMUL @ x6 with HSI (8MHz) but 6x8 = 48MHz ?

If I output the sysclk on a MCO pin (with no div) I have actually 24MHz.

After use of SystemCoreClockUpdate() from system_stm32f0xx.c the variable SystemCoreClock equals to 48000000 and my call to SysTick_Config(SystemCoreClock/1000) gives a wrong systick frequency ( 2 x too slow, the actuel sysclock is 24000000).

In the reference manual RM0360 at the figure 11 I see no div /2 between HSI and PLLSRC for my STM32F030xC.

But the behaviour

seems like in the figure 10, with a /2 ....

Where is the mistake ?

Thanks

Peter

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-28 8:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-30 8:26 AM

Hi

Miles.Peter

,Please check the content ofRCC_CFGR2: is PREDIV set to '0001' or '0000'?

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-25 4:05 AM

Hi Amel,

Sorry for my late reply. But it is still a mystery for me, I checked the PREDIV of the RCC_CFGR2 and it is '0000'.

So I have tried with RCC_CFGR2 set to '0001' and even '0010', but it has no effect on the output frequency still at 24MHz with my

PLLMUL @ x6.

On the other hand I am able to read these values in debug mode with atollic and it seems this register is well programmed.

The behaviour is really like a STM32F030x6 and not a STM32F030xC .

Is it a bad interpretation of the reference ? My chip is marked as STM32F030RCT6. Is it a x6 or a xC ???

Thanks for your help.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-13 7:54 AM

Hi

Miles.Peter

,Sorry to come back to this discussion so late.

I would like to inform you that we made the test from our side using the same configuration as yours to output SYSCLK on MCO. The output frequency is 48 MHz.

To continue investigating the issue,could you please share the content of both registers RCC_CFGR and RCC_CFGR2?

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-28 7:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-28 8:37 AM

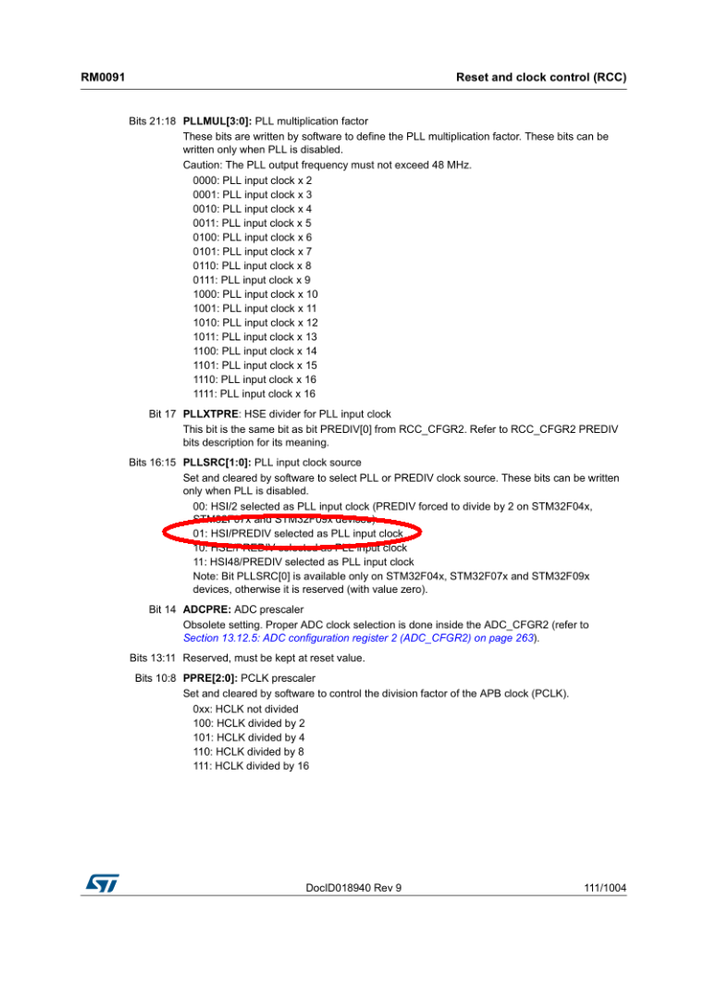

Use this setting:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-28 9:16 AM

Hi Jan,

your document is RM0091 but the ref. manual for my STM32F030RCT6 is RM0360.

In the RM0360 there is a HSI/2 selection as PLL input in the register description, but not in the figure 11. That is what I don't understand and what doesn't match with my C drivers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-28 9:39 AM

I know.

Just try.

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-28 10:48 AM

Thanks

Miles.Peter.001

for sharing these inputs.Could you please also check that DEV_ID value is 0x442 and REV_ID value is 0x1000? [read DBGMCU_IDCODE, address 0x40015800].

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-28 11:08 AM

void CORECheck(void) //

mailto:sourcer32@gmail.com

{ uint32_t cpuid = SCB->CPUID; uint32_t var, pat;printf('CPUID %08X DEVID %03X REVID %04X\n', cpuid, DBGMCU->IDCODE & 0xFFF, (DBGMCU->IDCODE >> 16) & 0xFFFF);

pat = (cpuid & 0x0000000F);

var = (cpuid & 0x00F00000) >> 20;if ((cpuid & 0xFF000000) == 0x41000000) // ARM

{ switch((cpuid & 0x0000FFF0) >> 4) { case 0xC20 : printf('Cortex M0 r%dp%d\n', var, pat); break; case 0xC60 : printf('Cortex M0+ r%dp%d\n', var, pat); break; case 0xC21 : printf('Cortex M1 r%dp%d\n', var, pat); break; case 0xC23 : printf('Cortex M3 r%dp%d\n', var, pat); break; case 0xC24 : printf('Cortex M4 r%dp%d\n', var, pat); break; case 0xC27 : printf('Cortex M7 r%dp%d\n', var, pat); break;default : printf('Unknown CORE\n');

} } else printf('Unknown CORE IMPLEMENTER\n');}Up vote any posts that you find helpful, it shows what's working..

- STM32F3 DISCOVERY - PLL not behaving as expected in IAP code in STM32 MCUs Boards and hardware tools

- STM32F030CC IWDG and SPI1 doesn't work properly. in STM32 MCUs Embedded software

- RM0360 and stm32f030xc.h TIM7 IRQ discrepancy in STM32 MCUs Products

- CAN communication in STM32 MCUs Products

- Wakeup pins for STM32F030xC are missing in CubeMx in STM32CubeMX (MCUs)