- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- How long after increasing the clock rate do I need...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How long after increasing the clock rate do I need to wait?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 02:53 AM

Further to my previous question on the STM32L432KC at https://community.st.com/s/question/0D50X0000BAFA5fSQH/what-is-the-difference-between-these-two-clock-configurations

I am successfully increasing the clock rate from the reset rate of 4MHz to my desired rate of 80MHz (the maximum) using MSIClk synced to the LSE via the PLL. Part of that is waiting for the PLL to get lock - all of the status bits show everything is good to go.

Soon after, I configure USART1 to 115,200 bps (using PClk) and transmit a welcome banner. Unfortunately, the first few characters, from 0 to 5 of them, are corrupt. Once everything settles the data is perfect, but not the first few characters.

I added a simple `for (int i=0;i<10000;++i) asm(" NOP; ");` between setting the clock and sending the banner, and it's always perfect. If I reduce `10000` to `2000` it's often all right, but occasionally the first character is corrupt.

Is there a guaranteed way to know that the clock has stabilised before trying to use it?

Solved! Go to Solution.

- Labels:

-

RCC

-

STM32L4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 04:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 03:17 AM

I don't know the L4xx in detail.

> ... using MSIClk synced to the LSE via the PLL.

MSI is not a good choice for a stable and precise clock. It is based on an on-silicon RC element prone to manufacturing tolerances and temperature drift. See the datasheet.

The startup is usually associated with a power transient (peripherals are turned on, core begins to work), and switching the core clock from 4MHz to 80MHz as well.

Your problem might well be MSI temperature drift.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 03:25 AM

According to the datasheet, MSI does drift - but if you lock it via the PLL to the 32.768 kHz LSE (which I have), it's accurate enough to be used for USB work. So it's certainly good enough for serial comms.

But even if I were to use another clock, how do I know that that clock has settled? The reset rate is 4 MHz, and I want 80 MHz: when do I know that it's steady?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 04:33 AM

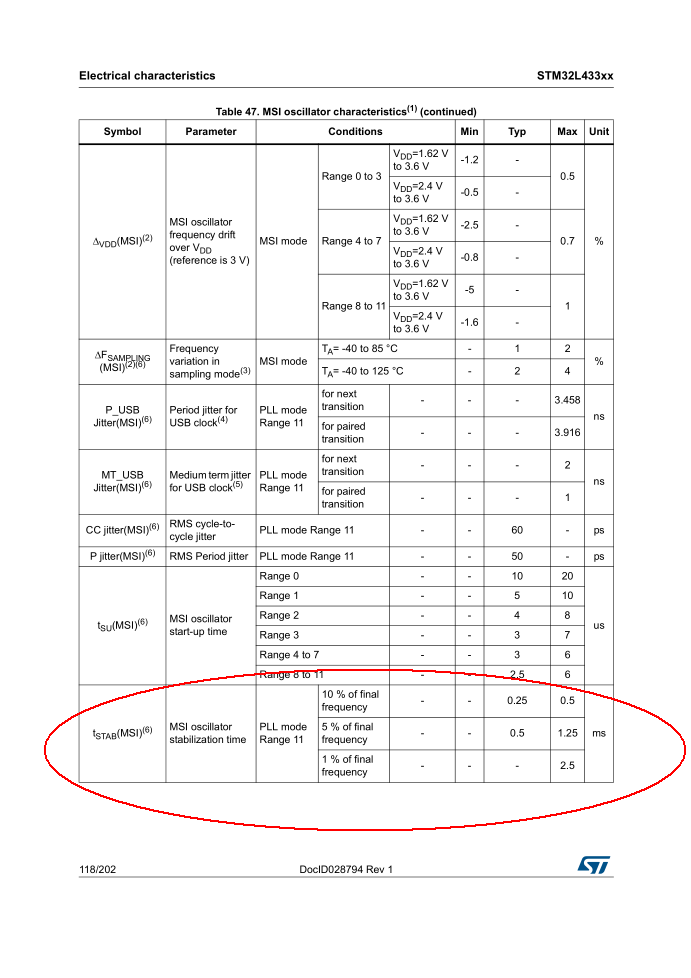

This is for 'L433, look in to DS for your device:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 04:40 AM

JW,

Perfect! Thanks a lot. The L432 has the same entries in its table - which I never even thought to look at!

John

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 11:03 AM

Rather than wait a fixed amount of time for MSI to stabilize, follow this advice from the Reference Manual:

"The MSIRDY flag in the Clock control register (RCC_CR) indicates wether the MSI RC is stable or not. "

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 11:13 AM

IMO the MSIRDY flag indicates stabilization after switching MSI on, i.e. is related to the tSU(MSI) parameter in the table I posted above; rather than to the stabilization of the PLL locking MSI to LSE.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 05:39 PM

@jerry2 Thanks, but I already do this - as JW said, after turning MSI on. Nevertheless I added the same wait code after doing everything else to increase the clock speed: no difference.

But yes, I'd prefer to check a register than wait some maximum time. Ah well!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-18 02:28 PM

Ah, I see, you want to know when the PLL is locked. Monitor Bit 25 PLLRDY in RCC_CR. When it transitions from 0 -> 1 the PLL is locked.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-18 05:25 PM

And I do that too. In fact, you have to do it before syncing the MSI to it. The last bit of my clock speedup code looks like this:

RCC_CR.PLLON = true; // Turn PLL (back) on

while (!RCC_CR.PLLRDY) { // Wait for it to turn on

} // while

RCC_CR.MSIPLLEN = true; // Sync MSI to PLL (requires LSERDY!)

RCC_CFGR.SW = SysClk_PLL; // Now switch SysClk to PLL

while (RCC_CFGR.SWS!=SysClk_PLL) { // And wait...

} // whileIt's after this code has finished that I still have to wait ~2ms before the clock has sped up enough to give reliable serial comms. Well... 5% after ~1ms may be good enough.

- BLE advertising stops randomly when going in stop2 mode in STM32 MCUs Wireless

- STM32WBA52 ADC Maximum Clock Frequency & Max Sample Rate at 12-Bit Resolution in STM32 MCUs Wireless

- STM32l0 stop mode and I2C slave: over consumption when disconnecting SDA (before scl) in STM32 MCUs Embedded software

- STM32N6570-DK AI demo not working in STM32 MCUs Boards and hardware tools

- STM32U575 GPDMA1 Configuration Problem in STM32 MCUs Products