- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Configuring NUCLEO-H755ZI-Q at 480MHz

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Configuring NUCLEO-H755ZI-Q at 480MHz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-28 9:23 AM

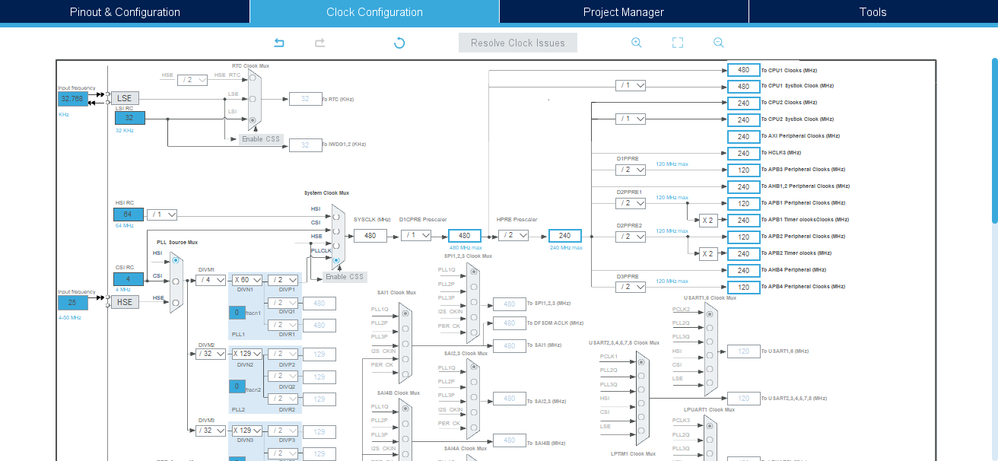

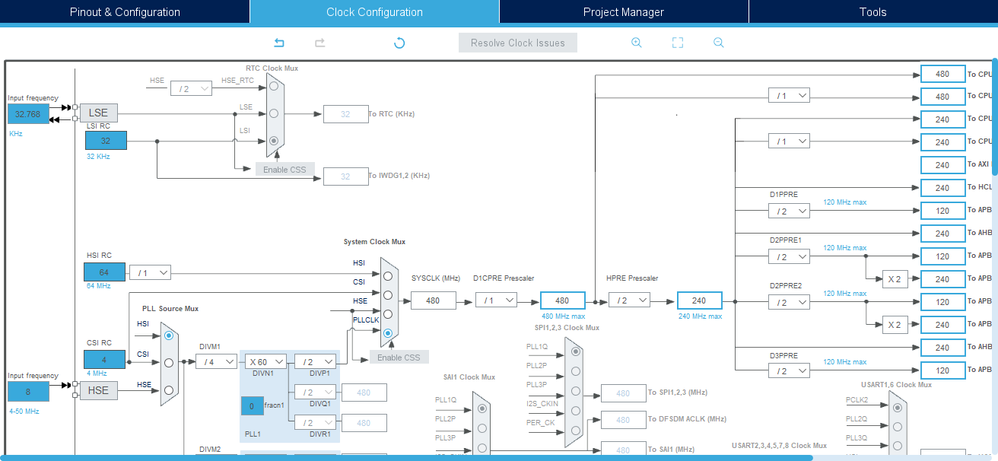

I'm trying to configure NUCLEO demo board at 480Mhz but I'm not able in any way, the following clock configuration seams to be correct, no conflicts

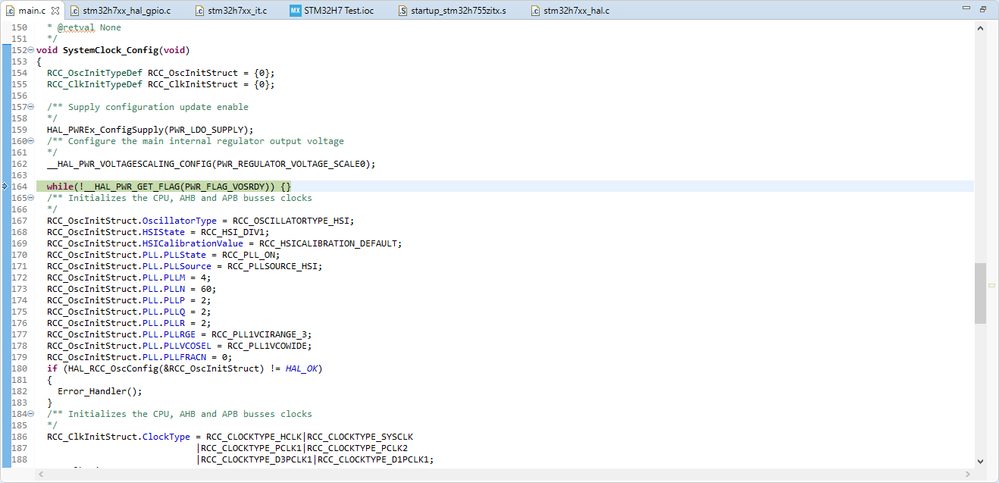

But the code will permanently hang on on the following configuration line

If I comment the line

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY))all seams to work correctly, why?

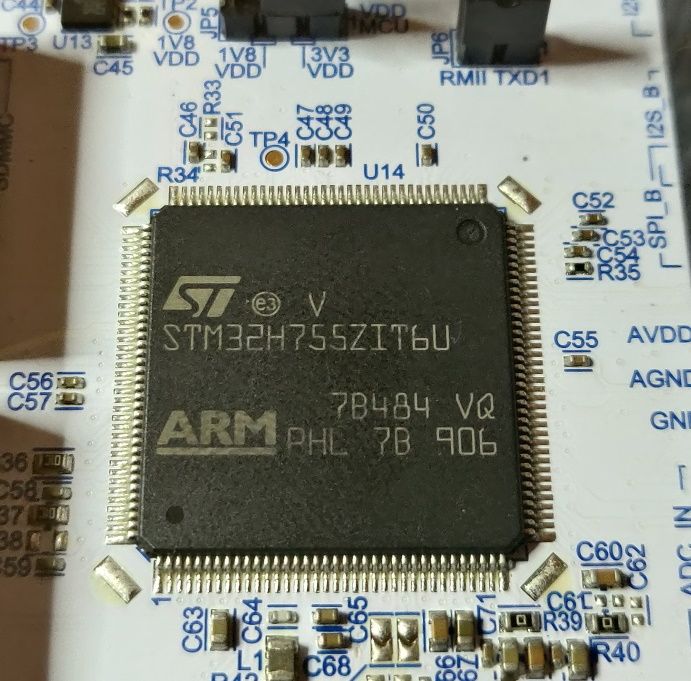

Chip revision seams to be V so It will be capable of 480MHz

What is wrong? Can someone post a correct clock configuration ? Is there a modify to the board to do? I'm using the last STM32CubeIDE 1.3.0 with H7 1.7.0 support library

best regards

GMG

- Labels:

-

RCC

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-28 1:57 PM

I've got Y step parts that run >500MHz

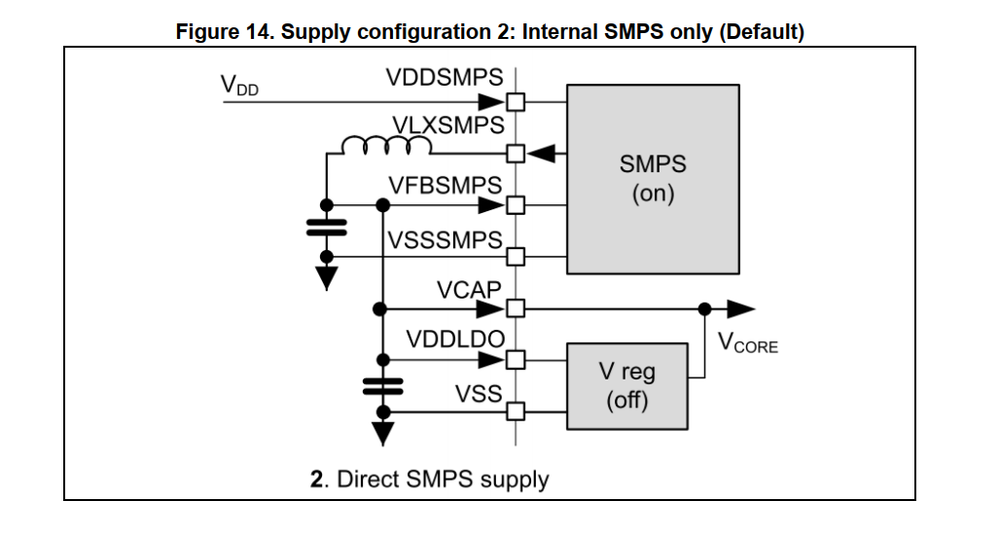

Check if it is wired for a SMPS supply?

STM32Cube_FW_H7_V1.7.0\Projects\NUCLEO-H745ZI-Q\Examples\PWR\PWR_VOS0_480MHZ\CM7\Src\main.c

/* The voltage scaling allows optimizing the power consumption when the device is

clocked below the maximum system frequency, to update the voltage scaling value

regarding system frequency refer to product datasheet. */

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {}

__HAL_RCC_SYSCFG_CLK_ENABLE();

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE0);

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {}

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-28 11:11 PM

Clock configuration on the STM32H7 using CubeMX has not worked reliably for me. However the RCC chapter in the reference manual gives usable instructions for setting up the clock tree.

This is for a STM32H743ZI on a Nucleo board. Check the steps in your reference manual, the H755 might require some additional steps.

void Systemclock_Config_480(void) {

// Enable the SYSCFG clock in the RCC by setting the SYSCFGEN bit in the RCC_APB4ENR register.

RCC->APB4ENR |= RCC_APB4ENR_SYSCFGEN;

PWR->CR3 = PWR_CR3_LDOEN;

while(!(PWR->CSR1 & PWR_CSR1_ACTVOSRDY))

;

PWR->D3CR = PWR_D3CR_VOS; // 11: VOS 1

while((PWR->D3CR & (PWR_D3CR_VOSRDY | PWR_D3CR_VOS)) != (PWR_D3CR_VOSRDY | PWR_D3CR_VOS))

;

SYSCFG->PWRCR = SYSCFG_PWRCR_ODEN; // VOS 0

while((PWR->D3CR & (PWR_D3CR_VOSRDY | PWR_D3CR_VOS)) != (PWR_D3CR_VOSRDY | PWR_D3CR_VOS))

;

RCC->D1CFGR =

(0b0000u << RCC_D1CFGR_D1CPRE_Pos) | // 0000: 0xxx: sys_ck not divided

(0b0100u << RCC_D1CFGR_D1PPRE_Pos) | // 100 : 100: rcc_pclk3 = rcc_hclk3 / 2

(0b1000u << RCC_D1CFGR_HPRE_Pos) | // 1000: rcc_hclk3 = sys_d1cpre_ck / 2

0;

RCC->D2CFGR =

(0b0100u << RCC_D2CFGR_D2PPRE2_Pos) | // 100: rcc_pclk2 = rcc_hclk1 / 2

(0b0100u << RCC_D2CFGR_D2PPRE1_Pos) | // 100: rcc_pclk1 = rcc_hclk1 / 2

0;

RCC->D3CFGR = 0b0100 << RCC_D3CFGR_D3PPRE_Pos; // 100: rcc_pclk4 = rcc_hclk4 / 2

RCC->PLLCKSELR = // PLLSRC=0 HSI

( 4u << RCC_PLLCKSELR_DIVM1_Pos) | // DIVM1 = 4

(32u << RCC_PLLCKSELR_DIVM2_Pos) | // DIVM2 = 32

(32u << RCC_PLLCKSELR_DIVM3_Pos); // DIVM3 = 32

RCC->PLL1DIVR =

((60u - 1u) << RCC_PLL1DIVR_N1_Pos) | // DIVN1 = 60

((2u - 1u) << RCC_PLL1DIVR_P1_Pos) | // DIVP1 = 2

0;

RCC->PLLCFGR =

// 11: The PLL1 input (ref1_ck) clock range frequency is between 8 and 16 MHz

(0b11u << RCC_PLLCFGR_PLL1RGE_Pos) | // ref1_ck=16MHz (HSI/4)

RCC_PLLCFGR_DIVP1EN | // PLL1 DIVP divider output enable

0;

RCC->CR |= RCC_CR_PLL1ON;

while((RCC->CR & RCC_CR_PLL1RDY) != RCC_CR_PLL1RDY)

;

RCC->CFGR |= RCC_CFGR_SW_0 | RCC_CFGR_SW_1; // select system clock source pll

while((RCC->CFGR & RCC_CFGR_SWS) != (RCC_CFGR_SWS_0 | RCC_CFGR_SWS_1)) // wait until clock source is ready

;

// now the system is running on 480 MHz.

}- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-01 1:01 PM

Hi, I think you may be right, now the problem is that I can't find a working solution to go to 480MHz using IDE configurator

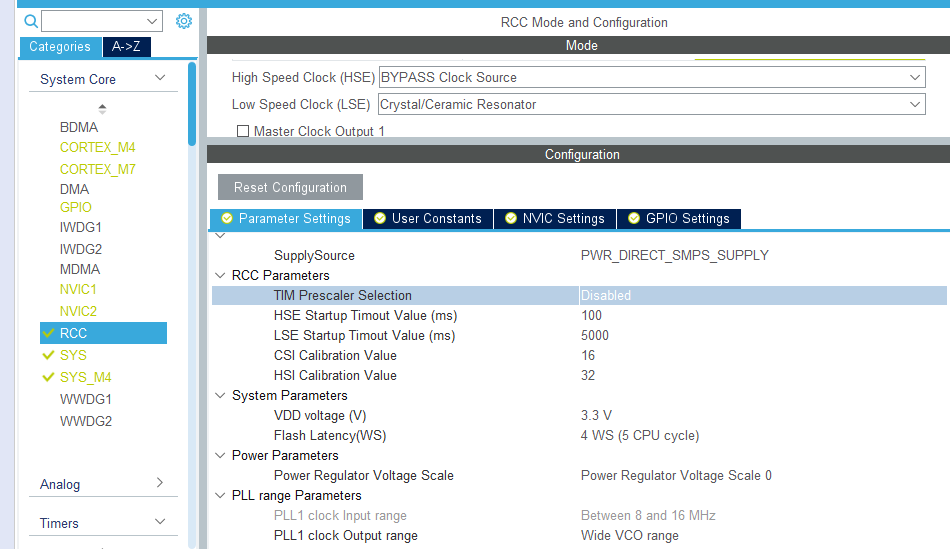

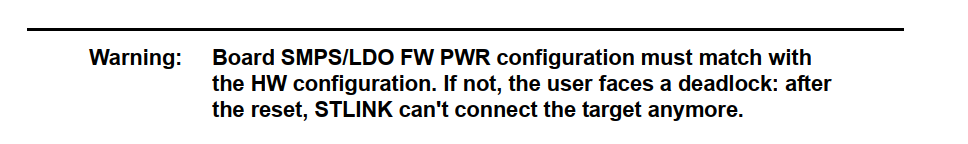

Board power configuration may be the default one as write in the user manual of the NUCLEO

Power Regulator Voltage Scale options can only be 0

The symptoms seem to be exactly those, but I don't understand how to solve it

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-12 10:25 AM

The problem was in the IDE, I was selected LDO and not SMPS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-04 11:25 AM

I know this is an old thread, thought I'd add a helpful tidbit. I had the darndest time getting the board to work at 480MHz, and when I got it (LDO, VC0) the board locked up when powering on. Once it was properly booted with a 240MHz build, I could flash the 480, and it would be fine until the next power cycle. So the solution is in the system clock startup, to start with the SMPS, then switch to the LDO. This worked on the stock Nucleo-H755ZI-Q board (rev V chip)

Use MX to configure for 480MHz (240MHz M4)(LDO, VS0), then in main.c, add:

/* USER CODE BEGIN Init */

// Start with SMPS before switching to LDO; necessary for 480MHz @ boot up

HAL_PWREx_ConfigSupply(PWR_DIRECT_SMPS_SUPPLY);

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE2);

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {}

/* USER CODE END Init */

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-17 10:29 PM - edited 2024-02-19 10:03 AM

@BKMY , thank you. It works!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-19 8:20 AM - edited 2024-02-19 8:31 AM

To all,

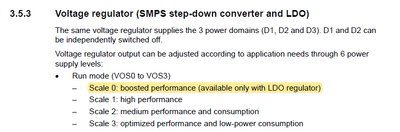

By specification VOS0 (480MHz max) can be reached only with LDO.

So no VOS0 with SMPS.

SMPS can reach up to 400MHz at VOS1:

Refer to the datasheet:

So with NUCLEO-H745ZI-Q the power configuration is SMPS => The max system clock is 400Mhz with this board except if you modify the board to be in LDO config.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-19 8:28 AM

I'm guessing either you didn't read and/or understand my posting. Without changing solder pad jumpers, when I set LDO/VS0, it works until power down/power up, at which point it locks up (race condition). By booting up and setting SMPS FIRST, and THEN switching to LDO, this lock up is prevented, and the 755 boots up like it should.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-19 8:36 AM

My comment was to all and especially to the the first question posted by GMG "Configuring NUCLEO-H755ZI-Q at 480MHz".

- STM32H723: How to achieve the Coremark figure? The published figure is 2778 at 550MHz. My implementation of Coremark at 480Mhz is a mere 327 with GCC ver10.3.1 and the default MX configuration. Is there an article on how to get full speed? in STM32 MCUs Products

- How to implement Full Duplex SPI communication in STM32H745 in blocking method? in STM32 MCUs Products

- STM32Hz MX Clock Configuration 480MHz in STM32CubeMX (MCUs)

- Why do I get overrun error when using DCMI? in STM32 MCUs TouchGFX and GUI