- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: FATFS DMA template problem on STM32H745iit6

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FATFS DMA template problem on STM32H745iit6

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-02 01:52 AM

Hello. I am trying to access SDMMC1 peripheral via Cortex-M4 core. I access SDMMC with no problem when I configure sdmmc clock 15MHZ or lower. Also fatfs use_dma_template option is disabled. But I have to use FreeRTOS in my project. So when i enable FreeRTOS, fatfs use_dma_template option sets to enabled automatically and i cant disable it. When use_dma_template option enabled, I cant access sdCARD or do any operation on it.

When i try to do exact samething for cortex m7, sdmmc enabled with 160 mhz, and freeRTOS enabled, i have no problem accesing, reading or writing. But with M4 problems occurs. How i can fix this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-03 12:11 AM

Update on problem : After some investigation, seems like M4 core cant use Internal DMA of SDMMC1. So it works only when HAL SD polling api used. (When dma template enabled, CubeMX uses dma api, which is not accesible to m4). I tried to use polling API in freeRTOS, but couldn't make it work. So i had to suspend the scheduler, to make it work. But suspending scheduler is not desirable for my application. Is there any work around of this. I saw some stuff about MDMA accessing SDMMC1 triggers. maybe that could be used? Any thoughts on this ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-03 07:59 AM

Hi @embeddedGeek,

Would you please share any project ,even dummy, that shows the problem?

regards

Haithem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-06 02:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-06 03:12 AM

Hi @embeddedGeek,

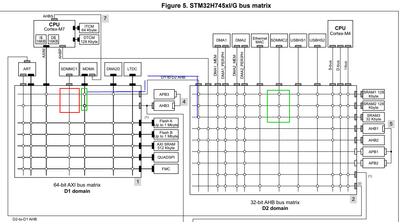

Looking at the STM32H745XX datasheet https://www.st.com/resource/en/datasheet/stm32h745zg.pdf

you can find the bus matrix description in the page 30.

As you can notice above SDMMC1/DMA does not have access to the Domain2 SRAMx memories as it is not connected to the D1/D2 AHB bus. it can only access the AXI SRAM in D1, same applies for SDMMC2 in the D2 that can't access the AXI SRAM in D1 but only the SRAM1, SRAM2 and SRAM3.

So to use DMA within SDMMC either work with CM7 & SDMMC1 or CM4 & SDMMC2.

otherwise you'll need to use polling mode.

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-06 03:22 AM

U mean Internal DMA of SDMMC or MDMA. What if i use AXI RAM for DMA and access with M4 to AXI RAM via ART by using D2-to-D1 AHB. I believe some trick could be done here to have multi core access to SDMMC1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-06 03:26 AM - edited 2023-11-06 03:32 AM

My ultimate goal is access SDMMC1 via both cores and solve abritarition with Hardware semaphores. I done it with bare metal system. But when It comes using freertos, CubeMX forces me to enable use dma template for fatfs. Thats makes SDMMC unaccessiable. But when i copy polling api sd_diskio.c files over my old files and suspend scheduler, i can access SDMMC from M4 again. But suspending scheduler is not desirable for my application. I wonder if there is any work around of this.

Also there is some flags for MDMA triggers. I wonder if i can use those to transfer data from AXI RAM to d2 rams to make it like working on D1 but copying some data(structures of fatfs, hal_sd and real data) to D2 rams. SO m4 can have pseudo access by triggering MDMA?

Also if use dma template not viable for m4 when accesing sdmmc1, when its there on cubemx. Thats should be a bug then?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-06 05:27 AM - edited 2023-11-06 05:28 AM

Hi @embeddedGeek ,

IIRC, your concerns is to perform SDMMC asynchronous transfers to avoid suspending the RTOS scheduler.

if this is the case then may be you can use the IT based API?

HAL_StatusTypeDef HAL_SD_ReadBlocks_IT(SD_HandleTypeDef *hsd, uint8_t *pData, uint32_t BlockAdd,

uint32_t NumberOfBlocks);

HAL_StatusTypeDef HAL_SD_WriteBlocks_IT(SD_HandleTypeDef *hsd, const uint8_t *pData, uint32_t BlockAdd,

uint32_t NumberOfBlocks);

These APIs are asynchronous and don't involve the DMA, i.e it is the CPU that initiates the transfer then waits for an transfer completion interrupt.

Does this help?

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-06 05:53 AM - edited 2023-11-06 10:54 PM

In that case, I have to update bsp_driver_sd.c and sd_diskio.c files. Is there any example for that ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-09 10:38 PM

Update : Still couldnt manage to make it work.

- STM32CubeMX v6.13.0 generates broken CMake project files for STM32U5 devices in STM32CubeMX (MCUs)

- Bug in MPU_AdjustRegionAddressSize breaks region maps if not already aligned in STM32 MCUs Embedded software

- Issues with STM32H750B-DK Board Bring Up For TouchGFX in STM32 MCUs TouchGFX and GUI

- stm32wb15 "CFG_LPM_STANDBY_SUPPORTED 1" does not work with BLE. in STM32 MCUs Embedded software

- HardFault_Handler when trying to add touch functionality in STM32 MCUs Boards and hardware tools