- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- JTAG lost after SystemClock_Config

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

JTAG lost after SystemClock_Config

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-05 11:00 AM

Hello,

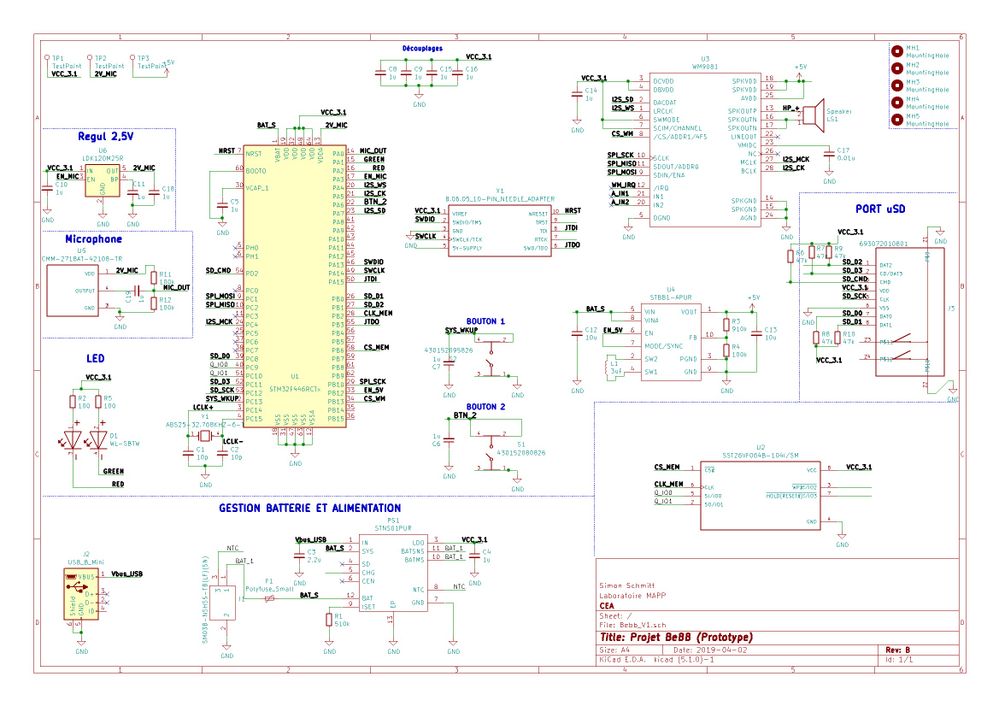

I'm currently working of a project based on a CubeMX generated code.

I'm currently experiencing something strange.

I use a Segger J-link as a programming interface. When I want to debug my program, as I can see, the program arrive inside "SystemClock_Config" function. I check that everything is ok with breakpoints and it don't seem to create error.

But after finishing this function the JTAG connection is lost like the board is disconnected.

I reproduced the problem at least 10 times to be sure it was not due to a bad contact on my board.

I would like to know if is some clock configurations can create this kind of problem.

Thank you,

- Labels:

-

Debug

-

STM32CubeMX

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-05 11:13 AM

Specific STM32?

Reprogramming GPIOA bank can be an issue, there might also be some settings to disable SWD/JTAG depending on how you configured CubeMX

Going into low power modes can also turn off the chip so the scan chains are not functional.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-05 11:21 AM

Yes, specific STM32.

What kind of low power features in CubeMX could cause that?

I double checked that JTAG was properly set in the configuration (JTAG 4 pins) and the GPIOA don't seem to have time to be modified at this time.

Thank you for your answer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-05 11:38 AM

What specific STM32 part, there's like a dozen families, and a hundred parts these days...

Not a CubeMX user, but remember a Debugger setting.

So bisect the executing code in SystemClock_Config() to pin down which section causes the failure, can't see what it's doing from here.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-06 12:11 AM

My bad. I understood your question as if I experienced this problem only with ST's MCU. Fatigue is the worst enemy.

It's a STM32F446RE.

I tried to debug the SystemClock_Config() function but nothing seemed wrong. I will try again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-08 3:40 AM

Hi @Community member ,

Please note that there is a limitation in STM32F4 devices where you cannot use Full JTAG configuration without NJTRST pin.

This is explained in errata sheet file.

So, JTAG 4 pins cannot be used and shouldn't be allowed from STM32CubeMX.

This will be reported to our STM32CubeMX experts.

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-13 7:58 AM

I checked in CubeMX and changing JTAG 4 pins to serial wire don't force me to use some unconnected pins of my design. So I think I will be able to use my J-Link with a ST-Link configuration in Atollic. Or worst case, I will have to wire the connector to my ST-link so it's just minimal pain.

Thank you,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-21 12:57 AM

Hello,

I'm back here due to the same kind of problem...

I've assembled my design with a new board (I corrected some mistakes which don't imply the uC) and now, the J-link can't even find the uC.

Here is the design:

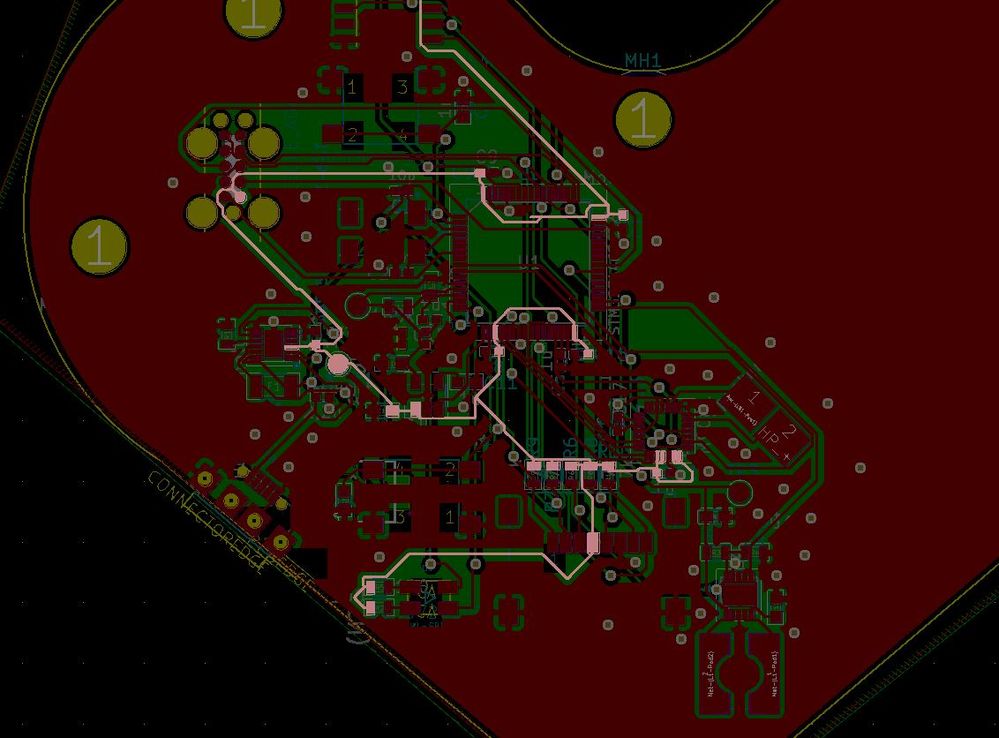

and here is the board:

What you see highlighted is the LDO 3.1V line from an STNS.

What I checked on my board with an oscilloscope is that JTDO is the only signal which don't seem to be properly driven. The signal is very noisy and I can perceive that it try to answer but the noisy signal just have a slightly higher average.

I tried to connect the Needle 10 pins to an ST-link and it don't work either.

If you have an idea...

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-21 2:15 AM

Well, You should read AN4488...

- VDDA is unpowered... And no - it's not only for ADC and DAC, but also internal RCs, PLLs, reset circuit and possibly something else.

- VCAP1 is wrong. It must be 4,7 uF and I suggest it to be at least 10V X7R 1206.

- VDD capacitors also doesn't follow recommendation - these should be 4,7 uF + 4 * 100 nF. I suggest 4,7 uF to be at least 10V X5R 0805.

- That long two part supply route is bad. Make a single branch for MCU and put recommended VDD capacitors to it.

- “Authentication Error Manager – Connection lost” in STM32CubeIDE (MCUs)

- “Authentication Error Manager – Connection lost” in STM32CubeIDE (MCUs)

- STM32CubeMX 6.17.0 generated project lost <root folder> in STM32CubeMX (MCUs)

- PRINTING not working when sending data to SWV ITM in STM32CubeIDE (MCUs)

- The list of #include in the main.c file is lost when regerating stm32cubemx with new GPIO config. in STM32CubeMX (MCUs)