- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs products

- Re: STM32MP15 ECO 5.0.0 OPTEE Panic set_clock_then...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32MP15 ECO 5.0.0 OPTEE Panic set_clock_then_voltage

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-14 11:47 PM - edited 2023-09-15 07:20 AM

On STM32MP1 discrete power. 512MB DDR , TF-A & OPTEE configure in SYSRAM

E/TC:0 0 Panic at core/arch/arm/plat-stm32mp1/cpu_opp.c:106 <set_clock_then_voltage>

Log attached.

This message seems to unique for stm32mp1 in OP-TEE code. no other platform source file seems to use this message.

Looking further this cpu_opp.c file is not part of OP-TEE on github in ST's stm32mp1 , thus ST unique and added afterwards to the ECO system. Seems to be patch. So that anyone familiar, outside ST, with what this code is doing is probably zero. The source does not reveal much about what is is doing. (no comments) w/o support this may take much more time to debug.

Move the regulator part in the DT (in root USER area) after the CPU clocks. Same result. what does ST's code expect ?

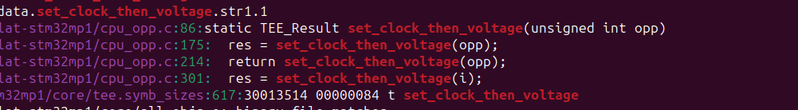

Added some debug traces:

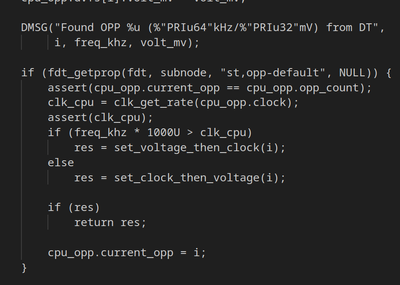

D/TC:0 0 stm32mp1_cpu_opp_get_dt_subnode:296 Found OPP 0 (650000kHz/1200mV) from DT

D/TC:0 0 stm32mp1_cpu_opp_get_dt_subnode:302 DEBUG: clk_cpu: 650000000

D/TC:0 0 stm32mp1_cpu_opp_get_dt_subnode:303 DEBUG: freq_khz: 650000

D/TC:0 0 stm32mp1_cpu_opp_get_dt_subnode:313 DEBUG: freq_khz*1000 <= clk_cpu. calling set_clock_then_voltage

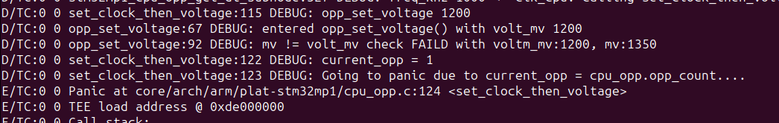

D/TC:0 0 set_clock_then_voltage:101 DEBUG: opp_set_voltage 1200

D/TC:0 0 set_clock_then_voltage:108 DEBUG: current_opp = 1

D/TC:0 0 set_clock_then_voltage:109 DEBUG: Going to panic due to current_opp = cpu_opp.opp_count....

E/TC:0 0 Panic at core/arch/arm/plat-stm32mp1/cpu_opp.c:110 <set_clock_then_voltage>

E/TC:0 0 TEE load address @ 0xde000000

E/TC:0 0 Call stack:

E/TC:0 0 0xde00e703

E/TC:0 0 0xde03da89

E/TC:0 0 0xde013d3b

E/TC:0 0 0xde0142bf

E/TC:0 0 0xde014397

E/TC:0 0 0xde03c3ab

E/TC:0 0 0xde03c799

E/TC:0 0 0xde03ccc7

E/TC:0 0 0xde03f5e9

E/TC:0 0 0xde00e425

E/TC:0 0 0xde00e52b

E/TC:0 0 0xde00019c

M/TC: CPU : 0

M/TC: usr_sp : 0x50044110

M/TC: usr_lr : 0x2080a000

M/TC: irq_spsr : 0x00071500

M/TC: irq_sp : 0x9200a48a

M/TC: irq_lr : 0x08500012

M/TC: fiq_spsr : 0xa28baa02

M/TC: fiq_sp : 0x50414465

M/TC: fiq_lr : 0x80282200

M/TC: svc_spsr : 0x00514014

M/TC: svc_sp : 0x0ac00264

M/TC: svc_lr : 0x41015450

M/TC: abt_spsr : 0xa0080800

M/TC: abt_sp : 0x55145c50

M/TC: abt_lr : 0x0280a280

M/TC: und_spsr : 0x3080c400

M/TC: und_sp : 0x00a8802a

M/TC: und_lr : 0x50454511

M/TC: pmcr : 0x2020a080

A voltage check if failing: it seems OPT-EE is expecting 1.2V instead of 1.35V for core ?

Solved! Go to Solution.

- Labels:

-

STM32MP15 Lines

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-15 04:34 AM

For some reason it requites this for vdd_core..

regulator-min-microvolt = <1200000>;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-15 03:48 AM - edited 2023-09-15 07:20 AM

Removed the CPU nodes in USER section, mentioned in workshop material, and that that causes an error even earlier in the boot. it seems the CPU nodes are needed in the DT. Perhaps they are missing some information ?

&cpu0 {

cpu-supply = <&vddcore>;

};

&cpu1 {

cpu-supply = <&vddcore>;

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-15 04:34 AM

For some reason it requites this for vdd_core..

regulator-min-microvolt = <1200000>;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 07:25 AM

Hi @debugging ,

Yes you are right.

You are using STM32MP157AAA3 which doesn't support overdrive mode @1.35V.

And even on part supporting it, this mode is not set in BSP but only at kernel level through opp_mode mechanism.

How to change the CPU frequency - stm32mpu

Olivier

In order to give better visibility on the answered topics, please click on 'Accept as Solution' on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 12:46 PM - edited 2023-09-19 12:47 PM

If not supporting overdrive at 1,35V is the reason, shouldn't setting regulator-max-microvolt at 1350000 also be an issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 09:42 PM - edited 2023-09-19 09:47 PM

Thank you for pointing out the mechanism for the issue.

It make sens Kernel manages speed and voltage setting, it would be similar to IPMI/ACPI. Though since this is a discrete board. Some questions:

1/ it seems OPTEE knows it needs 1.2V for this STM32MP157AAAC1 @ 650Mhz , Why would it have to panic. This DT entry could as well be removed or ignore instead of causing a panic. The code could also give a more explicit.For example" "Vdd_voltage core in DT not matching expected core voltage of X.XX". since this codes is ST specific, it is full under control of ST to add some improvements.

2/ How does one know which entries (for MPU power rails) to set in the DT for a specific MPU in TF-A, OPTEE and Uboot as well as the kernel in the "USER" areas..? Not only for power but also for clocks among others. A kind of "decision tree" based on the characteristic of the MPU and PMIC/discrete power would really make things much easier than reading through thousands of lines in WIKI's and PDF's to bring up a minimum viable configuration with and USB/SD boot and UART (serial debug.input I/O) to Linux.

3/ The informal trouble shooting guide and bring up WIKI for MP1 is more than 4 years old. Since then there should be many issues ST partners and customers walked into On the STM CN site there is a short one: https://wiki.stmicroelectronics.cn/stm32mpu/index.php?title=Visual_troubleshooting_grid&oldid=62487 but the link in that page to the "latest" , results in Page not found" Could ST put some effort in creating such guide ? Of-course not all situations can be covered. 20% of the of most common issues and common solutions could save 80% of developer's time. Many common issues can be found in the community If those could be linked to of most common causes, it may help a lot. And when new one's arise the page could be updated. "Common" should be al least 2 users having the same issue.