- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Embedded software

- Re: OPTEE header parse error on STM32MP135F-DK

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

OPTEE header parse error on STM32MP135F-DK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-10 03:01 AM - last edited on 2023-08-31 11:45 PM by Olivier GALLIEN

Hello,

I'm changing the DDR3 size from 512MB to 1GB on the STM32MP135F-DK board. The modifications were done as below. After that, I met the OPTEE header parse error. Compilation and updating software on board was conducted according to the ST wiki. ( https://wiki.st.com/stm32mpu/wiki/How_to_cross-compile_with_the_Developer_Package ) Please help me to solve this problem.

change from 0x20000000 to 0x40000000

- stm32mp135f-dk.dts in Linux Kernel, U-Boot, TF-A, and OP-TEE

- stm32mp135f-dk-fw-config.dts in TF-A

- stm32mp13-ddr3-1x8Gb-1066-binF.dtsi in TF-A (DDR_ADDRMAP6 0x0F070707 ==> 0x07070707)

- conf.mk in OP-TEE

Thanks.

NOTICE: CPU: STM32MP135F Rev.Y

NOTICE: Model: STMicroelectronics STM32MP135F-DK Discovery Board

NOTICE: Board: MB1635 Var1.0 Rev.E-02

INFO: PMIC version = 0x21

INFO: Reset reason (0x35):

INFO: TF-A simple example hello

INFO: Power-on Reset (rst_por)

INFO: FCONF: Reading TB_FW firmware configuration file from: 0x2ffe0000

INFO: FCONF: Reading firmware configuration information for: stm32mp_io

INFO: Using SDMMC

INFO: Instance 1

INFO: Boot used partition fsbl1

NOTICE: BL2: v2.6-stm32mp1-r2.0(debug):()

NOTICE: BL2: Built : 07:56:58, Jul 28 2023

INFO: BL2: Doing platform setup

INFO: RAM: DDR3-1066 bin F 1x8Gb 533MHz v1.53

INFO: Memory size = 0x40000000 (1024 MB)

INFO: BL2: Loading image id 1

INFO: Loading image id=1 at address 0x30006000

INFO: Image id=1 loaded: 0x30006000 - 0x30006246

INFO: FCONF: Reading FW_CONFIG firmware configuration file from: 0x30006000

INFO: FCONF: Reading firmware configuration information for: mce_config

INFO: FCONF: Reading firmware configuration information for: dyn_cfg

INFO: FCONF: Reading firmware configuration information for: stm32mp1_firewall

INFO: BL2: Loading image id 4

INFO: Loading image id=4 at address 0xde200000

INFO: Image id=4 loaded: 0xde200000 - 0xde20001c

INFO: OPTEE ep=0xde200000

INFO: OPTEE header info:

INFO: magic=0x4554504f

INFO: version=0x2

INFO: arch=0x0

INFO: flags=0x0

INFO: nb_images=0x1

WARNING: The load address in optee header 0xfe200000 - 0xfe2792e8 is not in reserved area: 0xde200000 - 0xe0000000.

ERROR: OPTEE header parse error.

PANIC at PC : 0x2ffe82b9

Exception mode=0x00000016 at: 0x2ffe82b9

- Labels:

-

OP-TEE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-07 08:17 AM

Hi @JKim.2 ,

Sorry to come late in this thread.

We will soon release a wiki page addressing modification to be done while changing DDR Size.

It described reduction from 512 to 256MB but I'm sure it can be relevant for the opposite.

Please let me know if it help

Olivier

In order to give better visibility on the answered topics, please click on 'Accept as Solution' on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 12:22 AM

Hi Olivier,

Thank you for the news. I'm looking forward to it.

Best Regards,

Jeff

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-10 12:29 AM - edited 2023-09-11 05:16 AM

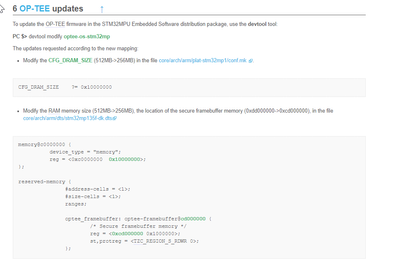

Have the same problem on a custom board. we had to change the memory to 0x400000 in OPTE DT to avoid OPTEE to stop compilation. If this was/is known issues, why is there no information ? Also, please advice a link to this the page of this picture ? Tried to Google some some the text in it,but can't find it. Was it recently added somewhere ?

In my case there is no 135f.dts file (using STM32MP157AAA3), Modifying the .mk file it keep gets overwritten back to the original value at the build. (perhaps it uses it from the dts file)

Just found a WARNING message in the OPTEE wiki, but this warning is not in the TF-A WIKI

https://wiki.st.com/stm32mpu/wiki/How_to_configure_OP-TEE

Enable TF-A configuration switch STM32MP1_OPTEE_IN_SYSRAM=1 for both TF-A BL2 and TF-A FIP images.

enable OP-TEE configuration switch CFG_STM32MP1_OPTEE_IN_SYSRAM=y

Question #1:

if this build switch is needed for TF-A for STM32MP15 why is it not in TF-A configuration wiki ? Was this wiki just added recently ? Can't help wonder how to have noticed the big warning blocks.

Question #2

CFG_STM32MP1_OPTEE_IN_SYSRAM=y . set this to y in build/conf.mk but it always changes back to "n" it seems the build/.conf get generates at build time, but from which file ? Where to set this option to "y", in which file ? and This should contain a typo as well, it should be CFG_STM32MP1_OPTEE_IN_SYSRAM ?= y , correct ?

Question #3

Why does CubeMX not generate the correct values in the DT ? for the memory and reservation?

Question 4:

Added the reservation in the DTS, but OPTEE errors with that it cannot parse the line:

st,protreg = <TZC_REGION_S_RDWR 0>;

Copied the section from :

.dts:45.18-19 syntax error

FATAL ERROR: Unable to parse input tree

Found the reason because it needed the defintion in #include <dt-bindings/soc/stm32mp-tzc400-macro.h> Why was that not mentioned ?

Question 5:

It seems that OPTEE build does not generate the correct header information, it it did there would not be an error from OPTEE to find the OPTEE data, correct ? For this, changed the entry point in optee-header_v2.bin manually to the one that OPTEE seems to expect as listed in the error. For example change two bytes FE00 to DE00. but this causes another error. How to calculate the correct value in the header ?

ERROR: Parse optee image failed.

ERROR: OPTEE header parse error.

----

I don't like the wiki's that keep changing on the fly. Why not publish a PDF/book of the wiki and update when there is a change ? Quite old skool, but its so much better for version changes and tracking !

NOTICE: DEBUG: stm32mp1_arch_security_setup

NOTICE: DEBUG: print_reset_reason

INFO: Reset reason (0x14):

INFO: Pad Reset from NRST

NOTICE: DEBUG: stm32mp1_syscfg_enable_io_compensation_finish

NOTICE: DEBUG: fconf_populate

INFO: FCONF: Reading TB_FW firmware configuration file from: 0x2ffe2000

INFO: FCONF: Reading firmware configuration information for: stm32mp_io

NOTICE: DEBUG: stm32_skip_boot_device_after_standby

NOTICE: DEBUG: stm32mp_io_setup

INFO: Using SDMMC

INFO: Instance 1

INFO: Boot used partition fsbl1

NOTICE: BL2: v2.8-stm32mp1-r1.0(debug):()

NOTICE: BL2: Built : 06:37:24, Sep 10 2023

INFO: BL2: Doing platform setup

INFO: RAM: DDR3-DDR3L 16bits 533000kHz

INFO: Memory size = 0x20000000 (512 MB)

INFO: BL2: Loading image id 1

INFO: Loading image id=1 at address 0x2ffff000

INFO: Image id=1 loaded: 0x2ffff000 - 0x2ffff1ea

INFO: FCONF: Reading FW_CONFIG firmware configuration file from: 0x2ffff000

INFO: FCONF: Reading firmware configuration information for: dyn_cfg

INFO: FCONF: Reading firmware configuration information for: stm32mp1_firewall

INFO: BL2: Loading image id 4

INFO: Loading image id=4 at address 0xde000000

INFO: Image id=4 loaded: 0xde000000 - 0xde00001c

INFO: OPTEE ep=0xde000000

INFO: OPTEE header info:

INFO: magic=0x4554504f

INFO: version=0x2

INFO: arch=0x0

INFO: flags=0x0

INFO: nb_images=0x1

WARNING: The load address in optee header 0xfe000000 - 0xfe03dbb8 is not in reserved area: 0xde000000 - 0xe0000000.

ERROR: OPTEE header parse error.

PANIC at PC : 0x2ffecfa5

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 06:18 PM - edited 2023-09-13 06:19 PM

ST posted the WIKI on Step 12

but it did not solve my problem

and appears to be related to

And questions 1 to 4 above still stand. (Item 5 was probably a mistake i changing the header manually)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-17 07:23 PM

Hi Olivier,

Thank you for posting the guidance. ( How to configure a 256MB DDR mapping from STM32 MPU Distribution Package - stm32mpu ) After the compilation, I need to copy the result files to SD card. Btw, according to the tutorial in ST wiki ( How to cross-compile with the Developer Package - stm32mpu ), I found the same "fip-stm32mp135f-dk-optee.bin" should be copied to the sdb5 partition three times as below. Could you please confirm the destination partition is correctly noted in the tutorial? It's hard to understand how it can work. Thanks.

Best Regards,

Jeff

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-18 06:15 AM

Hello Jeff, the FIP contains OP-TEE (incl. OP-TEE Devicetree), u-boot and u-boot devicetree. So as soon as you have updated all your modification in the final FIP. You only need to flash it one time.

If you are using Makefile.sdk to generate your component, every time you build, the FIP will be generated again with the new component changes.

You can use dd as you did to update your board or the cubeprogramer or the cubeIDE (build + update).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-18 06:20 AM

For the partition names, you can use: "ls -l /dev/disk/by-partlabel/" on your host Machine to verify the right names.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-18 11:10 PM

I ran in the not in reserved area issue again. Always compiled with DEBUG=1. After removing that an all other DEBUG command line options for OPTEE and TF-A, finally BL32 Extra 1 (id 😎 and 2 (id 9) were loaded.

Both TF-A and OPTEE need STM32MP1_OPTEE_IN_SYSRAM=1 on the build command line and OPTEE CFG_STM32MP1_OPTEE_IN_SYSRAM=y CHANGED (not added) in the optee conf.mk file .

This solution worked for me. YMMV. (hope did not confuse anyone else).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 06:48 PM - edited 2023-09-19 06:52 PM

Hello Bernard,

According to the initial error log, I set reserved-memory for optee as below. However, the bootlog still shows "TEE load address @ 0xde200000" with the TZC permission failure. Enabling STM32MP1_OPTEE_IN_SYSRAM didn't help. Please review the below boot log.

optee-os-stm32mp-3.16.0-stm32mp-r2/core/arch/arm/dts/stm32mp135f-dk.dts

reserved-memory {

#address-cells = <1>;

#size-cells = <1>;

ranges;

optee_framebuffer: optee-framebuffer@fd000000 {

/* Secure framebuffer memory */

reg = <0xfd000000 0x1000000>;

st,protreg = <TZC_REGION_S_RDWR 0>;

};

};

u-boot-stm32mp-v2021.10-stm32mp-r2/arch/arm/dts/stm32mp135f-dk.dts

linux-5.15.67/arch/arm/boot/dts/stm32mp135f-dk.dts

reserved-memory {

#address-cells = <1>;

#size-cells = <1>;

ranges;

optee_framebuffer@fd000000 {

reg = <0xfd000000 0x1000000>;

no-map;

};

optee@fe000000 {

reg = <0xfe000000 0x2000000>;

no-map;

};

};

Best Regards,

Jeff

NOTICE: CPU: STM32MP135F Rev.Y

NOTICE: Model: STMicroelectronics STM32MP135F-DK Discovery Board

NOTICE: Board: MB1635 Var1.0 Rev.E-02

INFO: PMIC version = 0x21

INFO: Reset reason (0x234):

INFO: TF-A simple example hello

INFO: IWDG2 Reset (rst_iwdg2)

INFO: FCONF: Reading TB_FW firmware configuration file from: 0x2ffe0000

INFO: FCONF: Reading firmware configuration information for: stm32mp_io

INFO: Using SDMMC

INFO: Instance 1

INFO: Boot used partition fsbl1

NOTICE: BL2: v2.6-stm32mp1-r2.0(debug):()

NOTICE: BL2: Built : 07:56:58, Jul 28 2023

INFO: BL2: Doing platform setup

INFO: RAM: DDR3-1066 bin F 1x8Gb 533MHz v1.53

INFO: Memory size = 0x40000000 (1024 MB)

INFO: BL2: Loading image id 1

INFO: Loading image id=1 at address 0x30006000

INFO: Image id=1 loaded: 0x30006000 - 0x30006246

INFO: FCONF: Reading FW_CONFIG firmware configuration file from: 0x30006000

INFO: FCONF: Reading firmware configuration information for: mce_config

INFO: FCONF: Reading firmware configuration information for: dyn_cfg

INFO: FCONF: Reading firmware configuration information for: stm32mp1_firewall

INFO: BL2: Loading image id 4

INFO: Loading image id=4 at address 0xde200000

INFO: Image id=4 loaded: 0xde200000 - 0xde20001c

INFO: OPTEE ep=0xde200000

INFO: OPTEE header info:

INFO: magic=0x4554504f

INFO: version=0x2

INFO: arch=0x0

INFO: flags=0x0

INFO: nb_images=0x1

INFO: BL2: Loading image id 8

INFO: Loading image id=8 at address 0xde200000

INFO: Image id=8 loaded: 0xde200000 - 0xde2792e8

INFO: BL2: Loading image id 2

INFO: Loading image id=2 at address 0xc0400000

INFO: Image id=2 loaded: 0xc0400000 - 0xc040f750

INFO: BL2: Skip loading image id 16

INFO: BL2: Loading image id 5

INFO: Loading image id=5 at address 0xc0000000

INFO: Image id=5 loaded: 0xc0000000 - 0xc00e453c

NOTICE: BL2: Booting BL32

INFO: Entry point address = 0xde200000

INFO: SPSR = 0x1d3

I/TC: Early console on UART#4

I/TC:

I/TC: Non-secure external DT found

I/TC: Embedded DTB found

I/TC: OP-TEE version: 3.16.0-dev (gcc version 11.3.0 (GCC)) #1 Fri 28 Jan 2022 02:28:18 PM UTC arm

I/TC: WARNING: This OP-TEE configuration might be insecure!

I/TC: WARNING: Please check https://optee.readthedocs.io/en/latest/architecture/porting_guidelines.html

I/TC: Primary CPU initializing

I/TC: WARNING: All debug access are allowed

I/TC: Platform stm32mp1: flavor PLATFORM_FLAVOR - DT stm32mp135f-dk.dts

I/TC: DTB enables console (non-secure)

I/TC: Primary CPU switching to normal world boot

optee optee: OP-TEE: revision 3.16 (d0b742d1)

U-Boot 2021.10-stm32mp-r2 (Sep 19 2023 - 02:51:33 -0700)

CPU: STM32MP135F Rev.Y

Model: STMicroelectronics STM32MP135F-DK Discovery Board

Board: stm32mp1 in trusted mode (st,stm32mp135f-dk)

U-Boot simple example

Board: MB1635 Var1.0 Rev.E-02

DRAM: E/TC:0 tzc_it_handler:72 TZC permission failure

E/TC:0 dump_fail_filter:417 Overrun violation on filter 0

E/TC:0 dump_fail_filter:420 Permission violation on filter 0

E/TC:0 dump_fail_filter:425 Violation @0xfabfffb0, non-secure privileged read, AXI ID 4a0

E/TC:0 Panic at core/arch/arm/plat-stm32mp1/plat_tzc400.c:77 <tzc_it_handler>

E/TC:0 TEE load address @ 0xde200000

E/TC:0 Call stack:

E/TC:0 0xde203cb5

E/TC:0 0xde21bc31

E/TC:0 0xde207b09

E/TC:0 0xde21b2f1

E/TC:0 0xde238c2b

E/TC:0 0xde200340

- STM32MP135: Boot stops if vdd or vdd_ddr defined as fixed-regulator to tf-a device tree in STM32 MPUs products

- STM32MP135: U-boot - No serial driver found in STM32 MPUs products

- Help Needed: Enabling Secure Boot on STM32MP157C - "ERROR: Secured chip must enable TRUSTED_BOARD_BOOT in STM32 MPUs products

- STM32MP157 using qt5 issue in STM32 MPUs Embedded software

- STM32CubeProgrammer won't launch on Ubuntu 20.04 machine in STM32CubeProgrammer (MPUs)