- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs TouchGFX and GUI

- Re: FSMC timing calculation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FSMC timing calculation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-02-08 05:40 AM

hello,

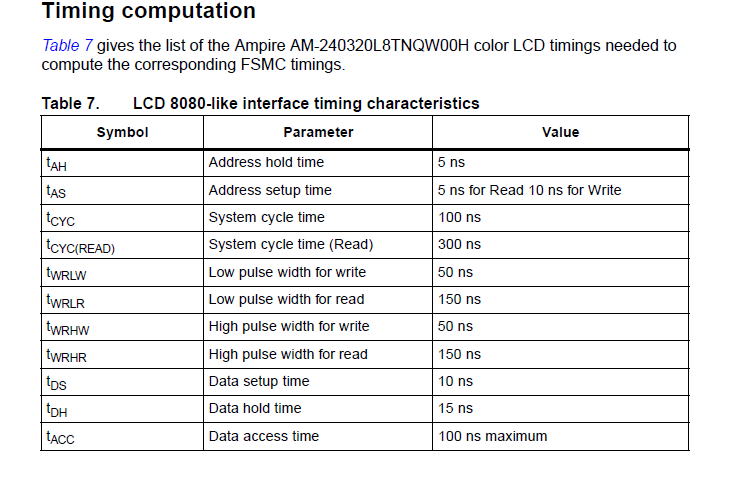

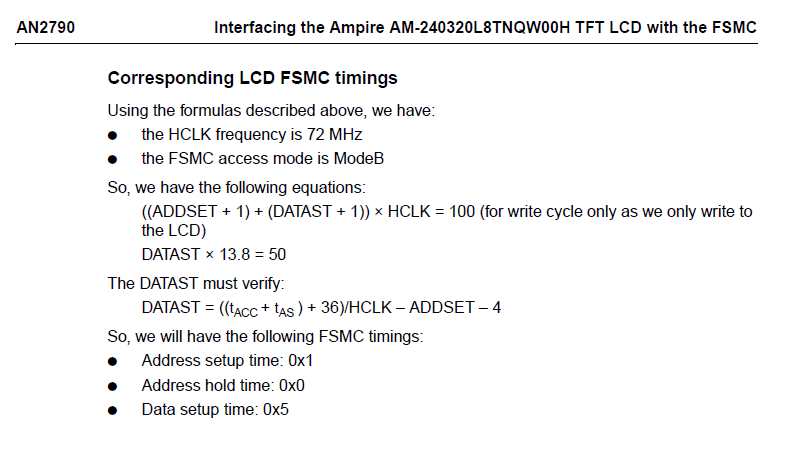

I want to interface SSD1289 lcd controller to stm32f103zet6 micro controller. I'm trying to understand the FSMC timing computations but to no avail. I referred to application note and found the following.

Could anybody please explain how these values are calculated. DATAST appears in equations for read and write. It will give two different values from these two different equations. SSD1289 has following timing characteristics. <<UNABLE TO POST IMAGE HERE, SO ATTACHING THOSE FILES>> I really don't know how to go about this. Isn't the tcycle-read(1000 ns) in above sheet too much. can FSMC handle that? I want to read and write to LCD. Kindly show me how to calculate the timing values. Thanks! #ssd1289 #stemwin #fsmc #stm32f1

Could anybody please explain how these values are calculated. DATAST appears in equations for read and write. It will give two different values from these two different equations. SSD1289 has following timing characteristics. <<UNABLE TO POST IMAGE HERE, SO ATTACHING THOSE FILES>> I really don't know how to go about this. Isn't the tcycle-read(1000 ns) in above sheet too much. can FSMC handle that? I want to read and write to LCD. Kindly show me how to calculate the timing values. Thanks! #ssd1289 #stemwin #fsmc #stm32f1

- Labels:

-

FMC-FSMC

-

STemWin

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-02-08 11:45 AM

The FSMC chapter in RM is far from clear and error-free, so it might require some experimentation. Also, I don't quite believe in the controller's requirement for 500/500ns RD high/low - you might have troubles to achieve quite that, OTOH the controller might not quite require it. It might quite well be that a total cycle time of 1000ns would be sufficient, and that might be achievable, given DATST is 8 bits long and 1000ns at 72MHz is 72 HCLK cycles. The other half of read cycle might perhaps be achieved as a combination of ADDSET and BUSTURN (and/or ADDHLD in mode D).

Nonetheless, separate read and write timing implies FSMC_BCRx.EXTMOD set. Then you set timing parameters for read in FSMC_BTRx, and for write in FSMC_BWTRx. JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-02-08 09:28 PM

Thanks JW! tried some values. Its working now. Although I still don't exactly know how to calculate them. Anyways, so long so good.

- Why is my SysTick timer not incrementing, causing no RPM calculation? in STM32 MCUs Products

- STM32H743 memory bandwidth issues with DCMI, FMC, ADC, parallel bus, DMA1, DMA2 / DCACHE issue in STM32 MCUs Embedded software

- FMC timing calculation for NAND Flash in STM32 MCUs Products

- How to calculate the Nand flash timing when I config the FMC for a nand flash? in STM32 MCUs Products

- SSD1963 Initialization in STM32 MCUs Products