- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- TImer triggered circular DMA SPI TX

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TImer triggered circular DMA SPI TX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-08 6:57 AM

Hi,

I am trying to understand DMAMUX possibilities and usage.

My target is to implement auto refresh of external muxed (scanning) SPI LED display. Just 3 shift registers in daisy chain. 1 byte selects current characters (mux) and 2 bytes are contents of those characters. Thus 3 bytes per display refresh. To implement varying digit brightness, 3 bytes turns on segments and next 3 bytes may or may not turn off segments (2 value duty cycle control).

I also need automatic NSS control. IRQ notification, when could be frame buffer updated (kind of vsync) would be nice.

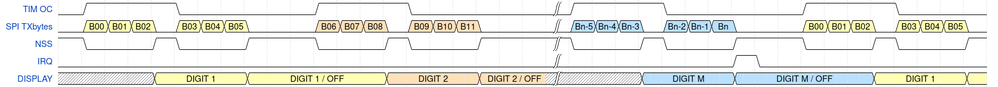

Here waveform of what I want to achieve:

(edit: fixed naming)

Is this possible with G0 DMAMUX?

Brightness control could be implemented differently.

Thanks,

Patrik

- Labels:

-

DMA

-

SPI

-

STM32G0 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-08 7:32 AM

Triggering 3 transfers (to SPI) should be possible, albeit the only timer which links to DMAMUX trigger is TIM14; but the fancy NSS waveform will be a challenge.

I'd perhaps try to pull this out differently, using a "normal" DMA to update the timer's registers to generate NSS on one channel, and "strobes" which would trigger DMA-to-SPI on other channel.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-08 8:45 AM

Interesting idea to generate NSS with timer, but how do I trigger "normal" DMA with timer output?

Also, I need DMA in circular mode with buffer size of m*3 bytes, but transfer only 3 bytes per trigger.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-08 10:03 AM

Timers can generate multiple DMA requests on a single event (see DMA burst mode and the DCR register). The trick is to use the DMA request from the timer update event to copy data to the SPI data register. SPI has a 32 bit FIFO, so it can take the 3 bytes of data at once. Then set up a timer output channel in PWM mode 2 to provide the NSS signal. In PWM mode 2, the signal goes low at the update event, and goes high at the compare event, which should be set to allow the 3 bytes to be shifted out.

Then a second DMA request from the same timer to a DMA channel that updates the timer period (ARR) could provide the variable length NSS signal. The problem is that it would generate bursts of 3 DMA requests as well, because the DCR setting applies to all DMA requests coming from that timer, so the data in the array of ARR values should be tripled. This can be avoided by using 2 timers in a master-slave configuration, the master provides the NSS signal, and the slave is just turning the trigger input into triple DMA requests.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-08 10:32 AM

Thinking about it, DMAMUX request generation could work with any timer output. As far as I know, EXTI works even if the pin is in output or alternate mode.

So you can generate any kind of complicated NSS waveforms that you can pull off with DMA and/or master/slave timer modes. Just ensure that the NSS low time allows for 3 bytes to be transmitted. Then set up the DMAMUX request generator to trigger on the EXTI falling edge on the timer output pin, sending 3 requests to a DMA channel that copies data to the SPI data register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-09 9:39 AM

> Thinking about it, DMAMUX request generation could work with any timer output. As far as I know, EXTI works even if the pin is in output or alternate mode.

>

> So you can generate any kind of complicated NSS waveforms that you can pull off with DMA and/or master/slave timer modes.

Sounds like a neat trick!

OTOH, I would be wary of the need to clear the EXTI interrupt, to produce another edge on the DMAMUX trigger input.

I don't use any chip with DMAMUX (yet); have a G0 EVAL sitting on my desk for around a year but haven't gotten to excercise it yet... :(

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-09 10:18 AM

If that's the case, then another DMA channel, triggered by the output compare event of the timer channel providing NSS, can take care of resetting EXTI.

- Touchgfx FreeRTOS and SAI I2S Master Integration in STM32 MCUs TouchGFX and GUI

- Switching from HAL to LL complications in STM32 MCUs Embedded software

- ADC readings in STM32 MCUs Products

- STM32H7 ADC HAL_ADC_ConvCpltCallback not called in STM32 MCUs Products

- External DAC SPI interface speed optimization in STM32 MCUs Products