- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32H755, is the clock too slow?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H755, is the clock too slow?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 02:10 AM

Hello everyone, I'm working on an STM32H755BI (industrial temperature range), and i'm quite disappointed by the maximum clock reachable from the system.

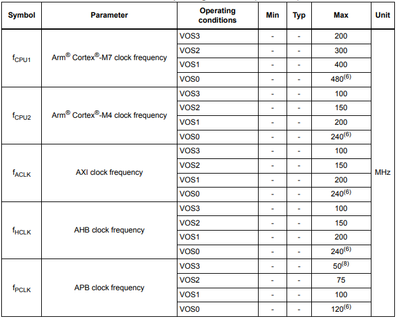

As can be seen, the MCU can reach up to 480MHz in the core M7 and 240MHz in the core M4.

After months of develpment, a firmware package update blocked me the VOS0 and VOS1, and in fact reading the user manual those modes are unavailable on my package, so i reduced to 300MHz and 150MHz

Today, with an update of cube MX, this error appeared in the clock tree:

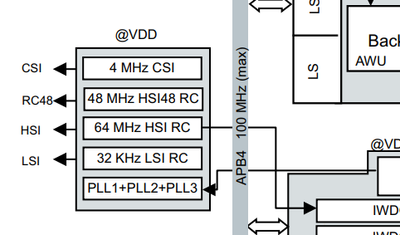

And in fact by reading the datasheet APB4 is limited to 100MHz.

Reducing APB4 to 100MHZ could not be a big deal, but the real problem is that considering the clock distribution in the previous image the clock of the APB4 is the same clock of the M4 (CPU2).

Does this means that i bought a 480+240MHz and i'm forced to use it at 300+100 after more than a year of development?

- Labels:

-

Power

-

RCC

-

STM32CubeMX

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-22 11:00 AM - edited 2024-02-22 11:06 AM

Is there any preclusion from running AHB4 at DIV1, where the M4 and M7 run at the same speed, synchronously? ie 200/200 MHz or 240/240

Or is it just a lack of creative thinking with regard to the operational frequency of the transistors and temperatures?

Are there critical paths in the M4 design, pipeline, prefetch paths and "caching" specifically exacerbated by temperature, or cause localized heating? Because it strikes me that there should be head-room above 240 MHz in the -40 to 85C, and as you derate the device to get to the broader temperature range are there some opportunities to balance this more effectively. This currently seems competitively crippling, for the sake of making the documentation and testing/characterization simpler.

Don't take this as a criticism, but more of a query of why something is being done or presented in a certain way. Looking for your thoughts and feedback.

Perhaps die level heat maps showing functional units, vs operating speed, or other supporting materials?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-23 09:53 AM - edited 2024-02-23 09:57 AM

Is there any preclusion from running AHB4 at DIV1, where the M4 and M7 run at the same speed, synchronously? ie 200/200 MHz or 240/240

I don't think there is a limitation where the M4 and M7 could run at the same speed.

It could be 240/240MHz or 200/200MHz.

Is there something that indicates this "limitation" in our documentation?

PS:

1 - This is NOT an online support (https://ols.st.com) but a collaborative space.

2 - Please be polite in your reply. Otherwise, it will be reported as inappropriate and you will be permanently blacklisted from my help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-26 12:54 AM

M4 and M7 can run at the same frequency with no problem, BUT:

If you use the M4 at 200/240 MHz (VOS0/1) you can use the M7 at 400/480MHz, no point of reducing the clock of the M7 at its 50%;

If you use (VOS2/3) The M7 can be used at 200/300 MHZ BUT the M4 cannot reach more than 100/150 MHZ, no reason to reduce the M7 to 100 MHz even in this case..

This is the "limitation" in your documentation, the VOSx settings. You are allowed to use the same frequency, but is meaningless.

- « Previous

- Next »

- slow hspi clock speed on STM32U5G9 in STM32 MCUs Products

- STM32U575ZIQ SPI behavior when enabling while slave select signal and clock are active? in STM32 MCUs Products

- STM32H7 errata sheet rev13 : new erratum about SPI not clear in STM32 MCUs Products

- STM32CubeMX: TSC Advice in STM32CubeMX (MCUs)

- STM32H745 input fast read in STM32 MCUs Products