- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32H755, is the clock too slow?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H755, is the clock too slow?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 02:10 AM

Hello everyone, I'm working on an STM32H755BI (industrial temperature range), and i'm quite disappointed by the maximum clock reachable from the system.

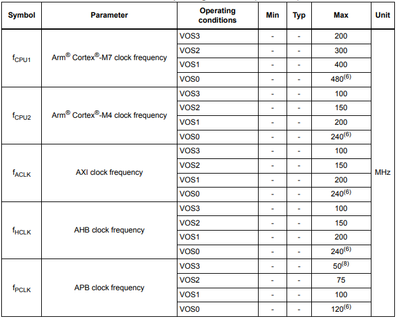

As can be seen, the MCU can reach up to 480MHz in the core M7 and 240MHz in the core M4.

After months of develpment, a firmware package update blocked me the VOS0 and VOS1, and in fact reading the user manual those modes are unavailable on my package, so i reduced to 300MHz and 150MHz

Today, with an update of cube MX, this error appeared in the clock tree:

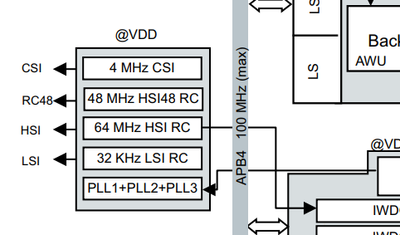

And in fact by reading the datasheet APB4 is limited to 100MHz.

Reducing APB4 to 100MHZ could not be a big deal, but the real problem is that considering the clock distribution in the previous image the clock of the APB4 is the same clock of the M4 (CPU2).

Does this means that i bought a 480+240MHz and i'm forced to use it at 300+100 after more than a year of development?

- Labels:

-

Power

-

RCC

-

STM32CubeMX

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 06:52 AM

>>On the other hand, there is this note in the datasheet which suggests the change was intentional

Without seeing what changed, I'd assume that relates to the 100 MHz for VOS3

Do you see a specific note that the M4 has to run at half-speed? AHB4 can be DIV1 as far as I can tell.

There is a lot of implied documentation that it is normative, but from a synchronous sense is it actually a necessity?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 06:59 AM

>>I also think that your pointed note refers to VOS3 (or at least i hope, since FCPU2 of 150MHz is allowed by cube)

That would be my read of it too.

I suspect CubeMX is applying VOS3 rules, not VOS2 rules. The gearing would look to permit 300+150 or 200+200

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 07:06 AM - edited 2024-02-13 07:10 AM

Me thinks it's a bug..

But I don't use CubeMX to build my clock trees.

The limits on the M4 are going to be critical path related in this context, running the transistors at 300 MHz isn't going make them run any hotter on the M7 vs M4 side of the die.

I've got Cortex-M3's running at 384 MHz on other processes, admittedly I don't have the FPU-S to contend with, but still.

Honestly I'd like to see a lot better analysis of where ALL these limitations are coming from. And what critical paths have been identified.

For example are there good reasons why 300+300, 250+250 or 240+240, etc aren't actually workable?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 07:37 AM

@Tesla DeLorean You are likely correct that the figure is from before the max frequency was bumped from 400 MHz to 480 MHz. Figure would be consistent with 400 MHz. Good catch on APB vs AHB, I should have caught that.

All that acknowledged, the underlying question remains the same. Datasheet clearly indicates 480/240 is possible on that chip, yet CubeMX doesn't allow it.

Underlying problem seems to be CubeMX doesn't allow VOS0 or VOS1 to be selected on STM32H755. Unclear why, probably a bug, but I could be missing something. They simply don't appear as options. No such issues on STM32H745.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 07:57 AM - edited 2024-02-13 08:04 AM

The basic "problem" is the allowed temperature range : -3 vs -6 , 125° vs 85° .

When 85° , 480/240MHz max., but at 125° 300/100MHz .

see

https://estore.st.com/en/stm32h755bit3-cpn.html

https://estore.st.com/en/stm32h755bit6-cpn.html

but wrong "promises" : > M7 core operates at up to 480 MHz ..< --- only for -T6 true !!!

And with -T3 only VOS2 or 3 allowed...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 10:53 AM

>> but at 125° 300/100MHz .

Ok where do you see this? VOS2 = 300/150, VOS3 = 200/100

It's stuff like this that I find fantastically UNHELPFUL

What I'd find helpful is the critical paths in the M4 implementation, and the transistor performance expectations at 125C externally vs junction temperatures.

There are SURELY better options for derated speeds, even with the unhelpful dividers.

If we knew where ST believed the critical paths were it would be possible to characterize, observe failure, and provide adequate safety margins. Or clock gear based on ADC_CHANNEL_TEMPSENSOR (ADC_CHANNEL_18)

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 11:20 AM

Buses at 240 and 120 MHz (readme talks of using LDO)

Here the FMC must be accommodated also

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 11:25 AM

Please check in CubeMX/IDE: RCC settings-> System parameters -> Product revision. Is it "V"?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 11:55 AM - edited 2024-02-13 11:56 AM

Sorry Clive,

I forgot ... just a footnote:

So here they set a limit - other than the "480 MHz " !

+ from ds H745 : if only VOS2 or 3 allowed ->

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-13 12:54 PM - edited 2024-02-13 12:57 PM

@AScha.3 When the MCU runs in the extended temperature condition, of course this text applies. But when it runs in "normal" conditions, nothing forbids you to set VOS0 and 480 MHz.

I've just created a new project in Cube for STM32H755BITx (x=3 or 6) and it allows to set VOS0. No problem.

The Cube itself does not limit anything. It's up to the factor that sits between the chair and the keyboard to decide how to set up MCU power and clock in certain runtime conditions.

- FMC with NAND Flash 8 times slower than expected in STM32 MCUs Products

- slow hspi clock speed on STM32U5G9 in STM32 MCUs Products

- STM32U575ZIQ SPI behavior when enabling while slave select signal and clock are active? in STM32 MCUs Products

- STM32H7 errata sheet rev13 : new erratum about SPI not clear in STM32 MCUs Products

- STM32CubeMX: TSC Advice in STM32CubeMX (MCUs)