- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32H743 SDRAM issues with LTDC + DMA2D

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H743 SDRAM issues with LTDC + DMA2D

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-16 01:30 AM - edited 2024-08-16 01:33 AM

Hello,

I'm trying to use a STM32H743XI to run a 1280x800px LCD display. I'm using an external 32bit SDRAM (IS42S32200L) running at 110MHz.

The active framebuffer (RGB565) is located in the first SDRAM bank and I can display a stable image with LTDC clock at 50MHz. However, as soon as I start to use the DMA2D (or another bus master) to write data somewhere else in the SDRAM, the display starts to show random flickering behavior (happens every few seconds):

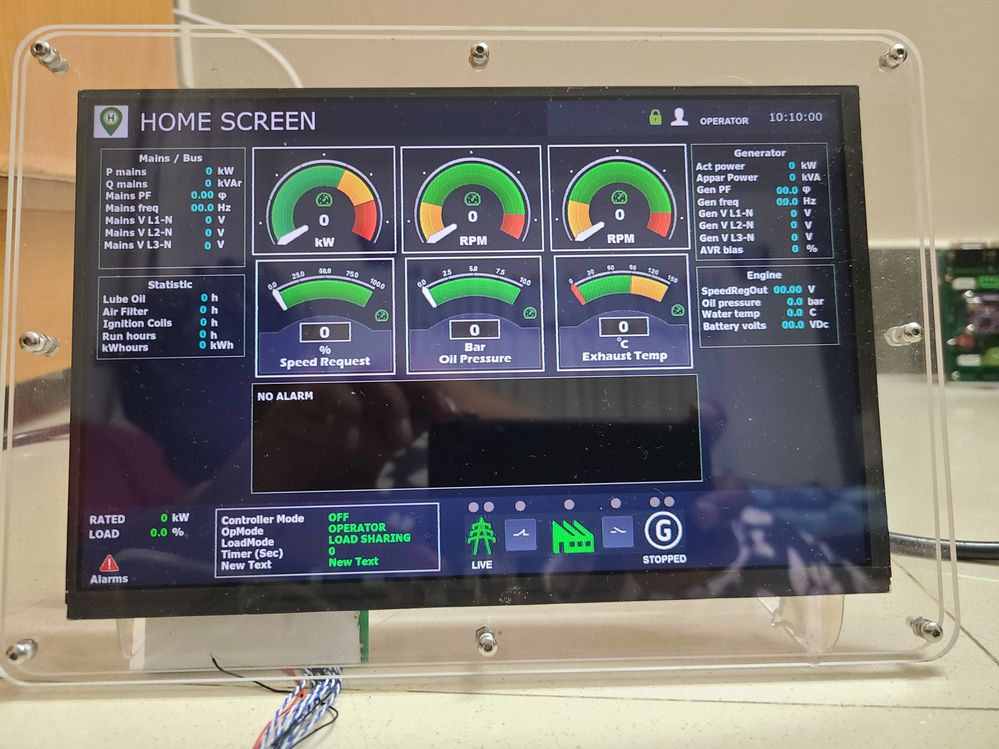

This is how the stable image looks like without flickering:

Lowering the LTDC frequency decreases the flickering occurence and below a certain point (around 30 MHz), the flickering effect stops completely. Timings from display datasheet specify min clock frequency of 66.3 MHz and with everything below 50 MHz, the image starts to become noticably unstable.

I have read AN4861 and from my understanding, my setup should work in theory given that my LTDC@50MHz is not even near the performance limit from this table:

I already tried the following things:

- Made sure that my backbuffer (where DMA2D is writing) is in another SDRAM bank

- Played around with AXI QoS prios -> little to no effect

- Disabled FMC bank 1 -> no effect

- Played around with DMA2D_AMTCR -> no effect, except that DMA2D takes longer

- Made sure that LTDC underrun interrupt is active -> never happens

Is there anything else I can try to optimize the LTDC performance? Is there something I'm missing? Can someone explain where these performance issues are coming from, even though everything should be well within the limits?

- Labels:

-

FMC-FSMC

-

LCD-LTDC

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-19 07:53 AM

Hi,

Please share Your project. Maybe I can help You. I have project with STM32H743BIT, external 16-bit SDRAM and display with resolution 1024x600. In my project I have enabled DMA2D, clock for LTDC is set to 50 MHz. I tested with TouchGFX and also with library LVGL. Performance is good.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-19 08:12 AM

Primary try sync updates in memory with display porchs + double buffer maybe. TouchGFX do it for you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-19 08:40 AM

Hi ..

almost 1.5 years ago , I used 1280X800 TFT with STM32H745 ,, and it worked quite fine with DMA2D .

Its SAMSUNG TAB3 10.1inch TFT (1280x800) with LVDS Interface.

following Core Board was used .

I designed my own custom dev. board for TouchGFX experiments.

share your project and I will try to be helpful.

regards

I.N

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-03 01:53 AM

Hello,

thank you for your suggestions! Sorry for the long delay, I was on vacation and unable to reply...

I intensified my search and tried a few more thing, but so far I'm unable to resolve the problem.

@MM..1I already tried to align the DMA2D to the display porches (as TouchGFX does it), this partially helps, but I run into performance contraints this way...

If I strictly stay inside the display porches, the flickering effect is no longer observable. But I need to display a 25fps MJPEG stream with 1280x720px, which means I have to update the whole backbuffer for every frame and this takes more time than I have in the display porches -> flickering stills happens

Also changing the MPU settings and trying to remap the SDRAM addresses has no real effect on the issue.

@INaee.1Thank you for your feedback. Your setup looks similar to what we have on our PCB.

At the moment I'm looking deeper into a possible hardware problem, maybe you can give some feedback on this? We also connected our LTDC RGB lines to a LVDS serializer for the display connector. When looking at the LTDC clock jitter (which is the input clock for the serializer), I can see that without any concurrent SDRAM operations, the LTDC clock jitter looks minimal. As soon as the DMA2D starts to write to the SDRAM, the clock jitter increases massively. I'm seeing something around 9ns (serializer chip allows for max 3ns of cycle-to-cycle jitter).

I also can see small pixel errors (wandering black pixels) on the left and right borders of the colored boxes in the image (happens in between the random flickerings of the whole screen)...

Is it possible, that the SDRAM load caused by the DMA2D write operation causes some kind of latency problems with the LTDC clock jitter and this in turn may lead to the problems on the display?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2025-02-01 05:22 AM

Hi @d.zipperle.5512730769682947E12

Sorry for long waiting .

I remain quit busy with some mechatronics projects so was not following the forum.

May I know , if your problem is solved ?

Here is my new experiment across Google Nexus 7 1st Gen , 7.0 inch TFT , 1280x800 resolution.

The Dev board is same as below .

regards

I.N

- STM32H743xI/G, STM32H753xI device errata and ST HAL implementation? in STM32 MCUs Embedded software

- Display Rotation Issue with GUIDRV_LIN_OSY_16 and Custom DMA2D FillRect Function in STM32 MCUs Embedded software

- Failed to start GBD server. No device found on target. in STM32CubeIDE (MCUs)

- Issue downloading the code on STM32H743 over JTAG interface in STM32 MCUs Products

- Issue occured after programming STM32H743 in DFU with STM32CubeProgrammer in STM32 MCUs Products