- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F42xx SPI errata handling with 70pF load

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F42xx SPI errata handling with 70pF load

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-20 11:12 PM

Hello

I was studying the errata sheet for my uC (STM32F427ZI) and found this entry:

Corrupted last bit of data and/or CRC, received in Master mode with delayed SCK feedback

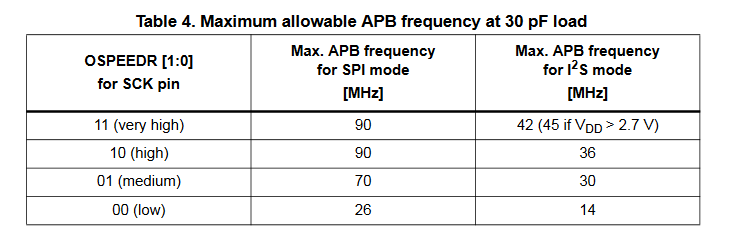

For the possible workarounds a table with the maximum allowable APB frequency is listed.

But my problem is, that on my SPI channel I have 70pF load. So now I don't know how to setup my SPI channel to avoid the corrupted last bit.

Does anybody have some informaton about this?

Kind regards

Mathias

- Labels:

-

Documentation

-

SPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-21 12:18 AM

Well, it's more-less an RC constant of the output transistor's full-open resistance and the load capacitance, which delays the SCK, so with OSPEEDR set on SCK to high you should restrain the respective APB to 90MHz/(70pF/30pF).

Or change the hardware design.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-21 01:41 AM

Thank your for your reply.

So you're saying, if I run the APB below 90MHz (which I do with 84Mhz) and set the OSPEEDR set on SCK to high I should be fine?

I would like to hear that with a clear statement from ST!?!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-21 04:00 AM

No. Actually I said that you should run APB below 90MHz/(70pF/30pF) = 38.6MHz.

> I would like to hear that with a clear statement from ST!!?!

Then contact ST directly. This is mostly a user-driven forum.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-21 04:09 AM

Oh sorry, somhow I missed the calculation :see_no_evil_monkey:

Thank you very much for your help.

I will ask ST directly about this problem.

- STM32H743 SPI4 MISO pin not receiving data in STM32 MCUs Products

- STM32H743 general VLAN handling not working as described in STM32 MCUs Products

- BUG with STM32H723ZGT6 in SPI1 SCLK on PG11 pin (missing) in STM32 MCUs Products

- I have a question,when changed cpu from stmf407 to stm32f427 .sometimes, read a wrong data from extern sram access by FMC ,it's happend in most of the cases in interrupt ,someone have the same problem? in STM32 MCUs Products