- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- I have a question,when changed cpu from stmf407 t...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

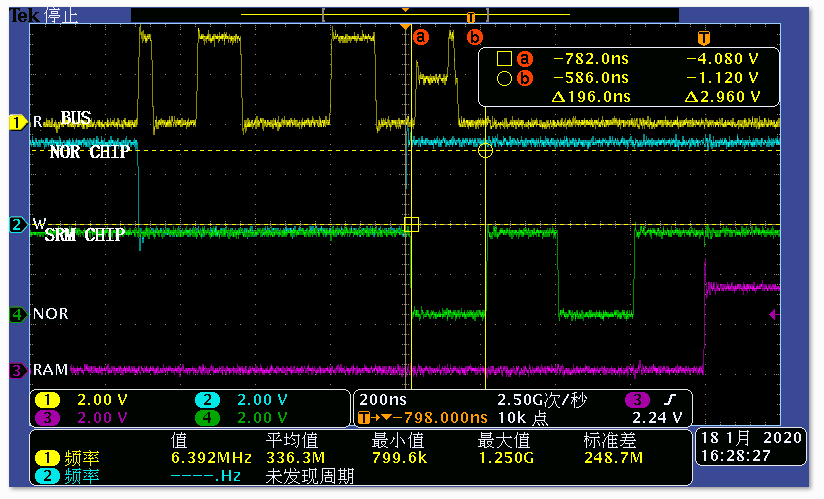

I have a question,when changed cpu from stmf407 to stm32f427 .sometimes, read a wrong data from extern sram access by FMC ,it's happend in most of the cases in interrupt ,someone have the same problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-15 12:06 AM

my English is poor,In the same program ,cpu 407 do not have this problem,only happened in 427,somtimes.It's like 2.3.4 Corruption of data read from the FMC. in <Errata sheet - STM32F42xx and STM32F43xx - STM32F427/437 and STM32F429/439 line limitations>,but it says ,This limitation is present only in revision “A�? devices. It is fixed in revision “Y�?, “1�?, “3�? and “5�? and “B�?. My revision is “3�?,there is someone have the same question?

/45

- Labels:

-

FMC-FSMC

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-15 2:32 AM

Can't this be a hardware problem, e.g. bad solder joint?

Is this still the same board, only with a different mcu?

And the system clock frequency did change or not?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-15 2:57 AM

Have you tried more conservative (slower) FMC timing settings with the F427 variant ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-27 7:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-28 12:14 AM

I don't quite understand the cause of your problem (appears to be both devices fighting for the bus, but why, once chipselects don't overlap?), but there are definitively differences in timing of FSMC in 'F40x and FMC in 'F42x, in what appears to be an identical setup https://community.st.com/s/question/0D50X0000C23GN6SQM/f427-fmc-vs-f407-fsmc-different-behaviour-for-backtoback-writes-to-the-same-sram-bank .

JW

- STM32G4 UART Signal Handler Error in STM32 MCUs Products

- STM32H7S3 - LDREX/STREX on Device memory - CMSIS bug in STM32 MCUs Embedded software

- PWM input output drift in STM32 MCUs Products

- SPI Comminication between two microcontrollers in STM32 MCUs Embedded software

- STM32H753ZI / MDMA issue with linked list (DMA ADC) in STM32 MCUs Embedded software