- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F412 SPI DMA data bit-shifted

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F412 SPI DMA data bit-shifted

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-29 04:15 PM

Hi.

First of all, the essence of my problem is already described here - https://community.st.com/s/question/0D50X00009XkiXu/spi-dma-data-corruption?t=1567119350874

In my case bug happens randomly and not very often. It could be one corrupted transaction among hundreds-thousands.

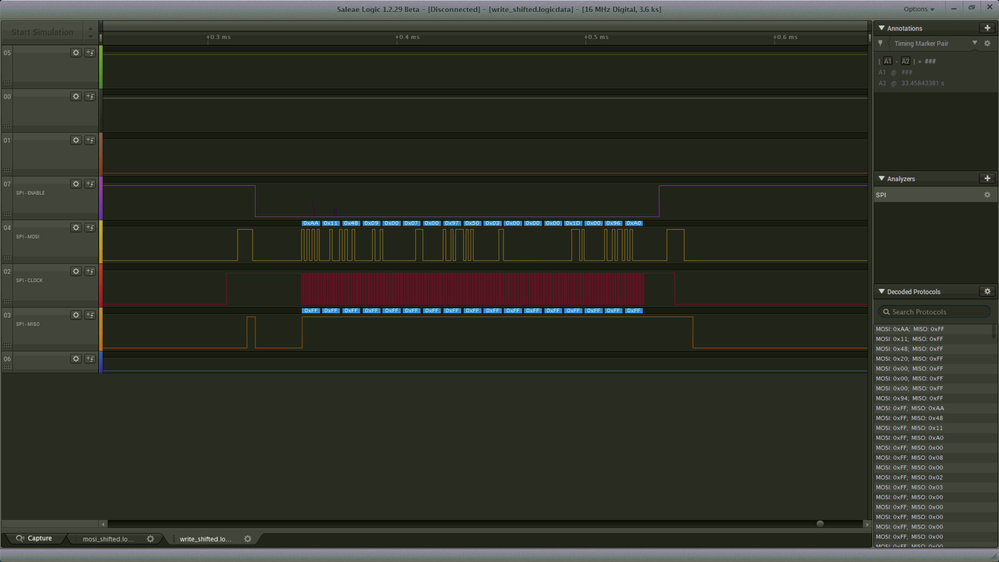

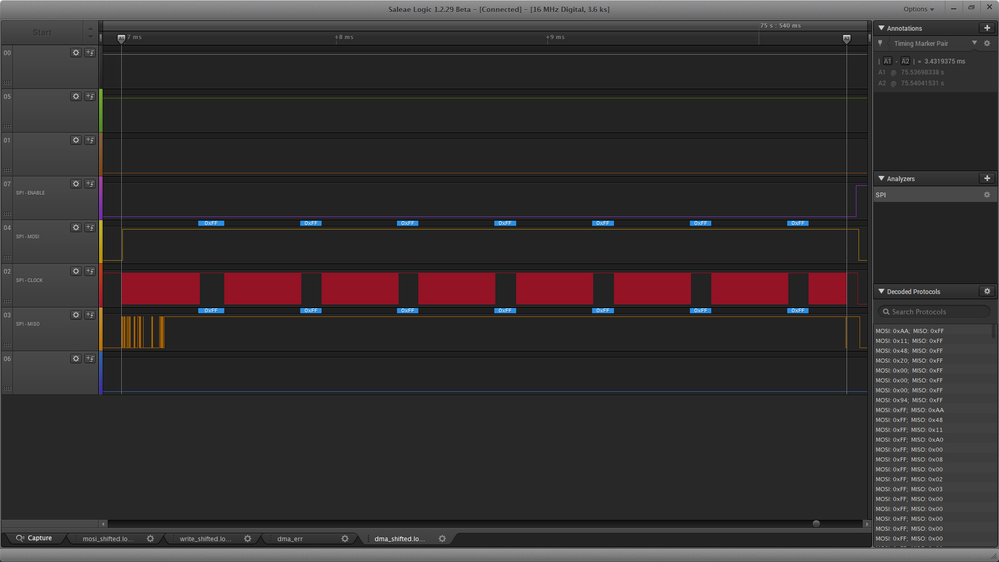

For example, how it is should work:

First byte always is 0xAA.

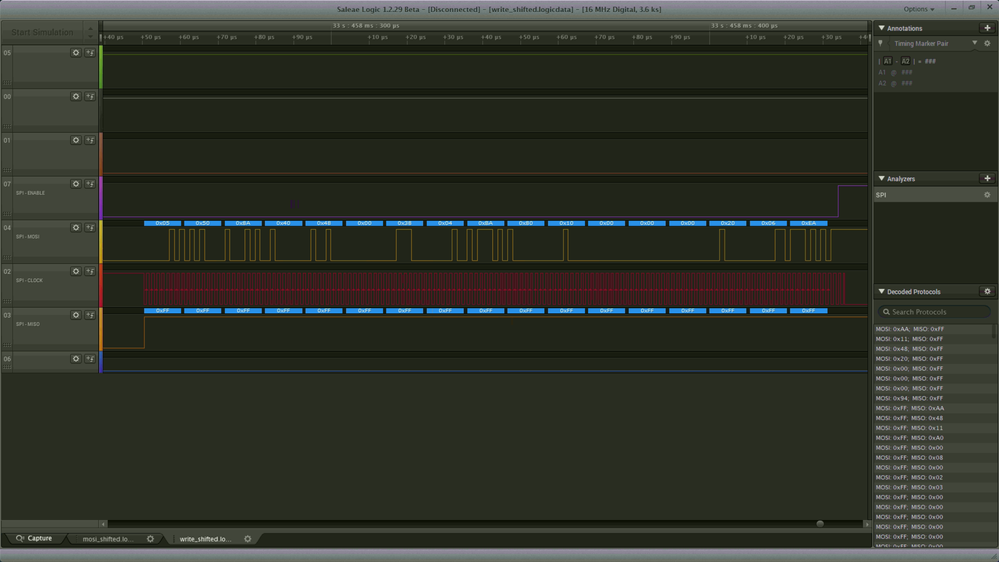

Here is an example of corruption:

You can see that CLK signal has already started, but data on MOSI is delayed by 5 bits (not constant, can be 4, 3...).

My code: https://pastebin.com/X3CfdH4q

And settings: https://pastebin.com/GKWTC1QH

- Labels:

-

DMA

-

SPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-30 12:03 AM

Read out and check or post content of SPI registers.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-30 03:29 AM

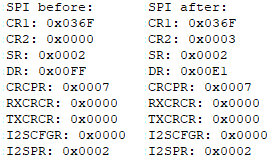

I have checked content before this calls:

SPI_I2S_DMACmd(spi, SPI_I2S_DMAReq_Tx | SPI_I2S_DMAReq_Rx, ENABLE);

DMA_Cmd(dma_rx_stream, ENABLE);

DMA_Cmd(dma_tx_stream, ENABLE);

And after end of transaction (DMA_IT_TCIF2 bit is set).

Data in DR register "after" - 0xE1.

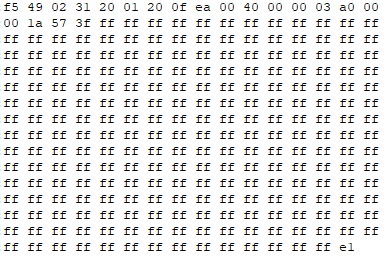

Content of RX memory buffer (should be AA 48 11 89 ..... FF FF FF FF):

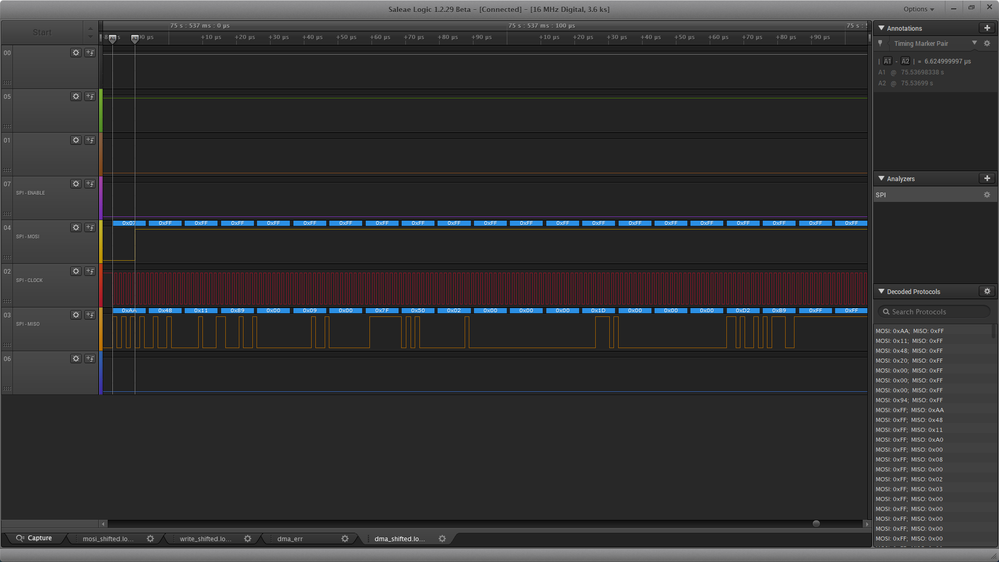

How entire transaction looks:

The beginning of it (in this case I send all 0xFF bytes):

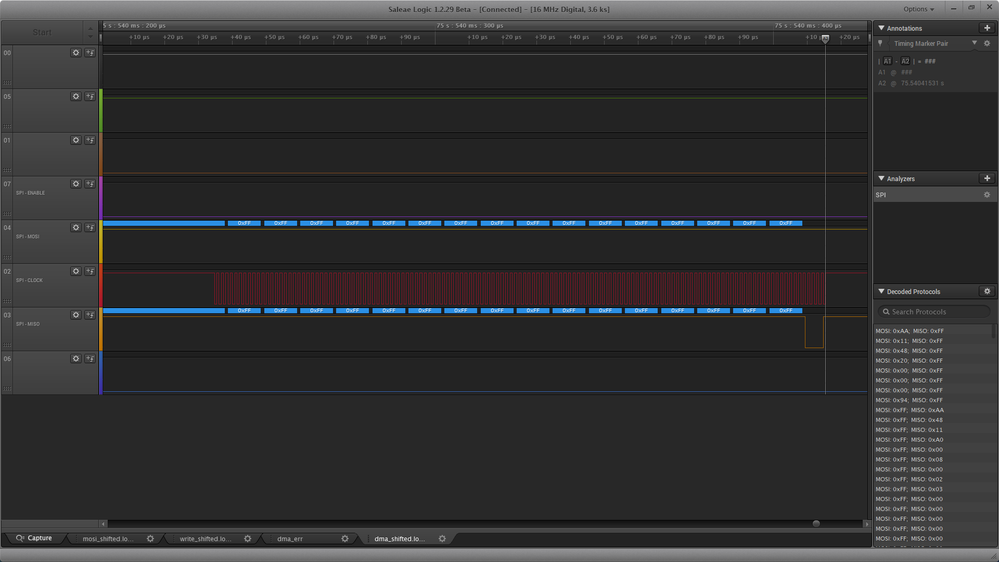

And the end:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-30 02:52 PM

Looks OK.

Does the transfer *before* the "failed" one exhibit any irregularity, e.g. incorrect/incomplete last byte transferred, or any outstanding clocks?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-31 05:15 PM

It seemed that you misunderstood me (or I don't understand you now).

There is no "before" and "after" transfers.

It is one transfer, I just read out SPI regs before DMA request and after end of the transfer (just in case).

Content of registers looks fine to me too.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-31 11:47 PM

> There is no "before" and "after" transfers.

You reset the whole mcu between transfers?

You've been talking about hundreds-thousands transactions. I don't believe you've performed hundreds-thousands system resets and observed single transfers between them.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-01 12:24 PM

When using DMA on SPI, you need to be careful in the timing and events. If here we are talking about SPI Master, my advice are:

- DMA TX main purpose is to generate the SCK clocks (and push out data). It should not have an interrupt nor callback

- SPI should be in bi-directional mode (the other ones have time contrains)

- DMA RX should be the one triggering the transfer complete and the next possible block transfer.

- Always set DMA RX before TX (which kicks in the clocks)

If some of these points are not covered, dig more in your code, or try modify the source accordingly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-05 01:06 PM

Yes, you are right. I didn't reset mcu.

The last transfer before corrupted one was fine, so as next after it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-05 01:19 PM

Yes, in my case mcu works as master.

- TX stream do not have neither enabled interrupt nor used callback.

- Yes, we use "SPI_Direction_2Lines_FullDuplex".

- DMA_IT_TC interrupt enabled for RX stream. DMA and SPI will disable after this interrupt is happened.

- Already done.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-05 05:24 PM

> The last transfer before corrupted one was fine,

How do you know? Post scope/LA pictures.

JW

- Problem on replacing MCU in STM32CubeIDE (MCUs)

- STM32F412 CAN Transmits unexpected data in STM32 MCUs Products

- STM32F412 I2C2 Busy flag keeps set in STM32 MCUs Products

- STM32CubeProgrammer 2.16 - cannot program MCU by USB in STM32CubeProgrammer (MCUs)

- EXTI0 double interrupt on one edge in STM32 MCUs Products