- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F407 Continuous Conversion Issue Using AD...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F407 Continuous Conversion Issue Using ADC and DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-13 04:25 AM

I am currently using ADC for continuous conversion. Below is my program.

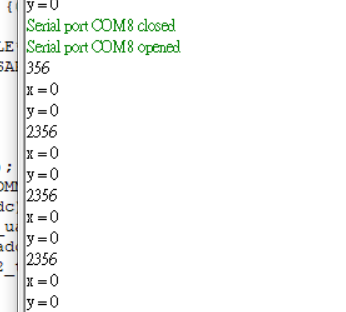

My ADC conversion is only successful after the first reset, and the Rxdata values are all zero.

Does any expert know where the problem is in my program?

- Labels:

-

ADC

-

DMA

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-13 06:49 AM

Rxdata should be defined as volatile.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-13 08:21 PM

Yes, you're right, here it should be changed to 0X1, but the result remains the same as before.

I've tried comparing it with mx, but still don't know where the problem is.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-14 06:49 AM

Rxdata should be defined as volatile.

> I've tried comparing it with mx

Keep trying. Show a screenshot with your values and the values from CubeMX. If one works and the other doesn't, there's a difference somewhere.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-15 06:55 AM - edited 2024-03-15 06:55 AM

Always start debugging peripherals by reading out and checking content of relevant registers - here, ADC and DMA.

If you'd do that, you would soon discover, that the DMA channel's CR does not have the enable bit set.

> //start

> DMA2_Stream0->CR |= (1 << DMA_SxCR_EN);

is incorrect, should be

//start

DMA2_Stream0->CR |= (1 << DMA_SxCR_EN_Pos);

As conversions were ongoing but DMA was not there to pick the data, ADC overrun and stopped (btw. for that reason you want to enable DMA before starting ADC).

JW

- adc continuous conversion with DMA for stm32f407G in STM32CubeIDE (MCUs)

- STM32F401 ADC VrefInt and Vbat read issue in STM32 MCUs Products

- STM32F411 continuous DMA from ADC, how? in STM32 MCUs Embedded software

- ADC Sampling Rate for STM32G431: Practical vs Theoretical measurements in STM32 MCUs Embedded software

- Two Serial ports with HAL_UARTEx_RxEventCallback don't work for me in STM32 MCUs Products