Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Inserting delay before synchronized pwm signal

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Inserting delay before synchronized pwm signal

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-18 03:01 AM

Posted on August 18, 2016 at 12:01

Hi All,

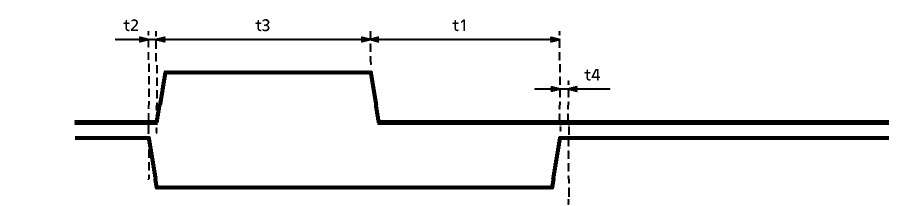

I have two signal, one high signal having 20% duty cycle and a low signal with 40% duty cycle. High signal is synchronized to low signal with reset trigger. I want to insert a delay of 100-400ns (t2 in diagram) before high signal so it looks like as in attached diagram. I tried to synchronized complementery pwm with dead time insertion but no success.

Labels:

- Labels:

-

TIM

1 REPLY 1

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-22 09:21 AM

Posted on August 22, 2016 at 18:21

Hi kumar.nitin.002,

Yes, you should insert a dead-time on complementary output signals OCx and OCxN of the same timer TIMx . There is no synchnoization to be done here. Just apply the same code of the ''TIM_complymebtarySignals'' example on the at this path: STM32Cube_FW_F3_V1.6.0\Projects\STM32F3-Discovery\Examples\TIM\TIM_ComplementarySignals You will have the OCx as the low signal (falling) and the complimentary high ignal (rising) with a delay. (in the example delay is : 100/SystemCoreClock (around 1.4us) ) -Hannibal-

Related Content

- Synchronize DMA to GPIO transfer on 2 distant MCU by external signal. in STM32 MCUs Products

- "Three phase" PWM for an LED "matrix" in STM32 MCUs Products

- Issue with SPI Data Reception in Receive-Only Mode in STM32L4 with DMA for ADC Data Capture - DMA Synchronization in STM32 MCUs Products

- Using STM32H7 SAI Slave Mode for USB Audio (UAC2.0) with DSD Format in STM32 MCUs Embedded software

- STM32WB OTA Reboot Failing in STM32 MCUs Wireless