Inserting delay before synchronized pwm signal

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-18 3:01 AM

Posted on August 18, 2016 at 12:01

Hi All,

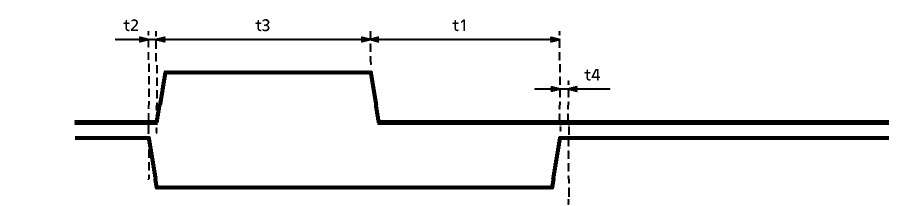

I have two signal, one high signal having 20% duty cycle and a low signal with 40% duty cycle. High signal is synchronized to low signal with reset trigger. I want to insert a delay of 100-400ns (t2 in diagram) before high signal so it looks like as in attached diagram. I tried to synchronized complementery pwm with dead time insertion but no success.

Labels:

- Labels:

-

TIM

This discussion is locked. Please start a new topic to ask your question.

1 REPLY 1

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-22 9:21 AM

Posted on August 22, 2016 at 18:21

Hi kumar.nitin.002,

Yes, you should insert a dead-time on complementary output signals OCx and OCxN of the same timer TIMx . There is no synchnoization to be done here. Just apply the same code of the ''TIM_complymebtarySignals'' example on the at this path: STM32Cube_FW_F3_V1.6.0\Projects\STM32F3-Discovery\Examples\TIM\TIM_ComplementarySignals You will have the OCx as the low signal (falling) and the complimentary high ignal (rising) with a delay. (in the example delay is : 100/SystemCoreClock (around 1.4us) ) -Hannibal-