- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: I2C multibus on alternative pins howto or is p...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2C multibus on alternative pins howto or is possible?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-17 8:13 AM

I ask for this , but any other same alternative use.

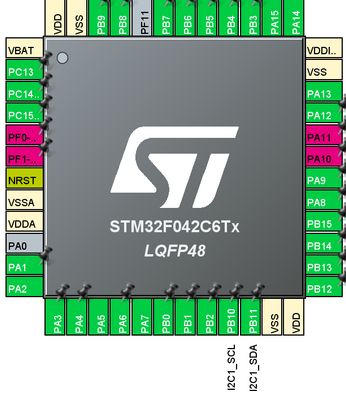

i set primary I2C on PB10,11 as on image an reserve PA10,11 and PF0,1

My plan is use alternative AF as I2C switch similar as IC PI4MSD5V9540

On PF pins is device on 5V I2C .

In code i try add to one I2C1 (have only one) PF pins when PB is active.

/**I2C1 GPIO Configuration

PF0 ------> DDC_SCL

PF1 ------> DDC_SDA

*/

GPIO_InitStruct.Pin = GPIO_PIN_0|GPIO_PIN_1;

GPIO_InitStruct.Mode = GPIO_MODE_AF_OD;

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;

GPIO_InitStruct.Alternate = GPIO_AF1_I2C1;

HAL_GPIO_Init(GPIOF, &GPIO_InitStruct);On scope seem signals is separated and address is send (HAL_I2C_Master_Transmit one byte) and ACK on PF pins, but no next data send. Seems somethink in HAL is broken after pin add.

When code deinit PB and only switch full pins to PF + init back com works ok.

Exist way to use more as one AF pin ?

- Labels:

-

STM32F0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-17 1:51 PM

I would not expect to be able to use PB10/11 **AND** PF0/1 at the same time as I2C pins. And why would you want to? That is not what the PI4MSD5V9540 does. It only enables one port at a time.

You certainly can enable PB10/11, talk to chips on those lines. Then disable PB10/11 and enable PF0/1 and talk to chips on those lines. As you've seen.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-17 2:02 PM

Would expect you could set ODR for pins HIGH, set the one you want to suspend into GPIO_MODE_OUTPUT_OD mode, and then the one you want to activate into GPIO_MODE_AF_OD

So a masked change (AND+OR) of the GPIO MODER registers

You'd want to make sure bus was idle/complete

The AF MUX doesn't have any catch fences about doing conflicting things, would just expect broken / undefined operation. A UART_TX might work out of two connection, not tried.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-18 6:56 AM

Seems trouble isnt OD mode, but input part, or input switching for ACK or slave. When is two port init , connection isnt dependent. Maybe i try search in reference manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-20 12:56 AM

Where i can find symbolic schematics for AF switching matrix?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-20 1:06 AM

Ok then better explain is PI4MSD5V9546A and why require ... for example price , less noise etc.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-20 1:11 AM - edited 2024-04-20 1:16 AM

You cannot have two I/O going to same unit ;

maybe sending on 2 switched together pins might work - but what should the chip do, with 2 pins going to one (internal) input , if A is hi and B is lo , for example ? Or two different responses coming in ?

As @Bob S and @Tesla DeLorean said, switching to one I/O pair and then to other (and back...) is possible and should work,

but not more than one input at same time to same internal input.

+

>Where i can find symbolic schematics for AF switching matrix?

see ds : pinouts ...alternative...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-20 1:44 AM

All this is ok , i try somethink undocumented. Table isnt schematics , but thanks

- USB OVER ETHERNET in STM32CubeIDE (MCUs)

- Issue with BOR Configuration on STM32G031F4P6 in STM32CubeProgrammer in STM32CubeProgrammer (MCUs)

- STM32G0B1 NRST not pinned? in STM32CubeMX (MCUs)

- errors in tutorial 4 in STM32 MCUs TouchGFX and GUI

- SBSFU/TFM debugging on M33 (U5) with TrustZone in STM32 MCUs Security