- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- FDCAN on STM32U5 and STM32H5 - serious FIFO/queue ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FDCAN on STM32U5 and STM32H5 - serious FIFO/queue and ID filter list size limitations

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-02 11:20 AM - edited 2023-12-05 1:57 AM

I am wondering if anyone notice that FDCAN on STM32U5 and STM32H5 MPUs has FIFO/queue size limited to 3 (three!) elements only.

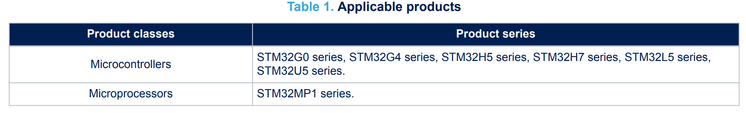

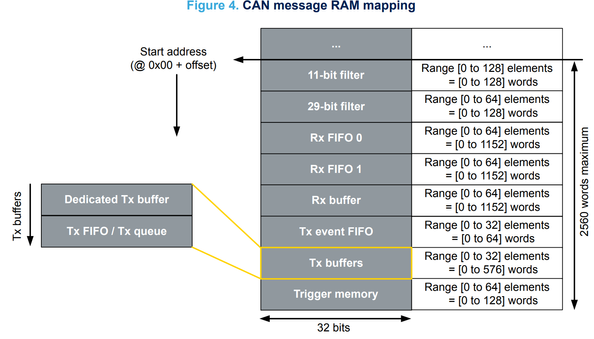

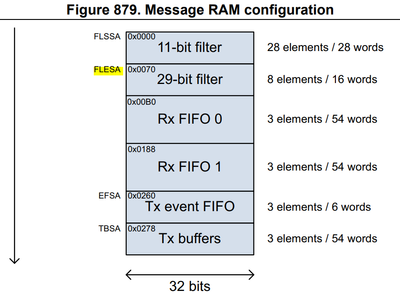

AN5348 - FDCAN peripherals for STM32 product classes does not mentioned that anywhere. The max FIFO/queue size discussed in AN5348 is very reasonable 64 elements. Consequently, all the FDCAN memory flexibility and RAM management discussed in AN5348 section 4.2 practically does NOT apply to U5, H5, G0, G4 and L5 families. Perhaps it applies to H7 family only. See FDCAN_RXF0S[F0FL] register description in the corresponding RMxxxx document. In particular, on STM32U5 FDCAN RAM config is fixed - (RM0456, Figure 879. Message RAM configuration). E.g. if you need just one RxFIFO buffer (FIFO0), you probably cannot use RAM reserved for FIFO1. and make it bigger. That is very unfortunate. One may think: OK, so I just configure selective hardware filters to catch only those messages I need, but one can configure just 8 'extended' 29-bit filters and memory reserved for 28 11-bit filters will remain unused. That is a pity, but that is not all. Rx buffers discussed in AN5348 section 4.3.2.2-4.3.2.3 just do not exist. The same is true Tx buffers, they do not exist. RM0456 in Figure 879 mentions them, but they mean Tx FIFO/queue only, not dedicated Tx buffers.

I do not want to call this 'false advertisement', but it came as a big surprise - especially for STM32U5 with plenty of SRAM. FIFO/Queue size limited to 3 elements perhaps would be bearable if I could use extended ID filter list (min 20 elements required) to receive only interesting NMEA2000 messages and avoid software filtering. However, I need to use classic filters (ID+mask) and only 8 extended ID classic filters can be defined. Dual or range filter is not an option. Functionality is there, it was just purposely and seriously limited in this supposedly top product for no apparent reason. It is just poor-man implementation and big STM32U5 disappointment.

Am I missing something? - see below

Fully configurable 10k FDCAN RAM documented in AN5348

The actual STM32U5 FDCAN fixed 848 byte RAM structure documented in RM0456

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-19 11:53 AM

I want to add my complains to the choice to use a so limited queue. It make totally no sense to have such limitation also in a Mcu like G4 or H5. What was the additional cost to put 32 elements instead of 4? We are not more in 1995.

And just update the documentation. From the general application notes it seems all the FDCAN equipped uC have the same capability but there is a reeeeeeally difference between H7 and "the others".

- « Previous

-

- 1

- 2

- Next »

- stm32 flashing via uart in STM32 MCUs Boards and hardware tools

- HSO Algorithm for STM32F4 or STM32F7 ? in STM32 MCUs Motor control

- STM32F412ZETx - CAN2 RX FIFO1 Interrupt Not Triggering (Tx Working) in STM32CubeIDE (MCUs)

- STM32H745XI: Software Jump to System Bootloader Without BOOT0/Option Bytes – Has Anyone Succeeded? in STM32 MCUs Products

- NPU SRAM in STM32 MCUs Products