- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: ADC sampling frequency - STM32H743ZIT

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC sampling frequency - STM32H743ZIT

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-01 02:28 AM - edited 2023-11-20 04:14 AM

Hi,

I use ADC3 on STM32H7, I need to know (and set) what is sampling frequency.

I use 3 channels in 16 bits.

What I tried to calculate?

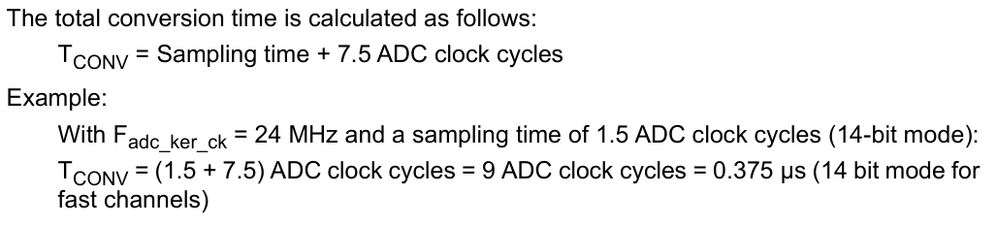

1) Tconv_time = 8.5(setable)+8.5(fixed for 16 bits) = 17 ADC clock cycles = 17/30Mhz = 566 ns

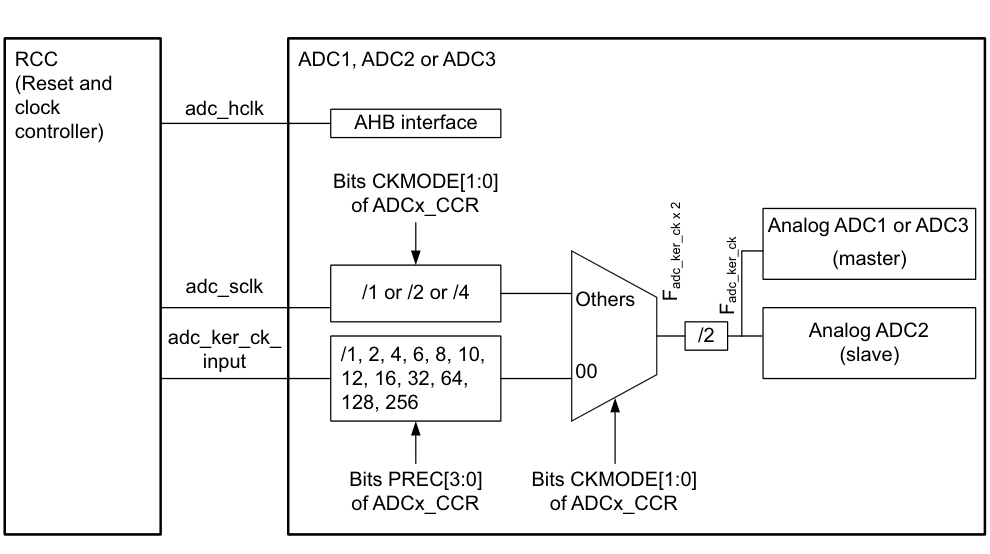

2) From this image I should have Fadc_ker_ck = 30 MHz, becase my CKMODE = 0b11, and adc_sclk = 480/2 = 240 MHz (HPRE=2) - so it is sys_clk/2

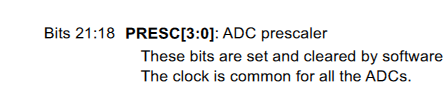

What about sampling frequency? My PRESC in ADC3_CCR = 0b1010 (divide by 128)

So I should divide some_CLK/128. What is the some_CLK? Is it the Fadc_ker_ck = 30 MHz?? Then it would be 30Mhz/128 = 234,375 kHz = 4,266 usec

Experiments:

I use BDMA for continual ADC3 measurement, I converts 200 samples for each chanels (3) = 600 samples.

I can measure the conversion time for all 3 channels - it takes 34.82 ms.

=> It is 600samples/34.82 ms => 1sample/58usec

So:

- measured time for 1 sample is 58 usec = 17,241 kHz

- calculated time for 1 sample is 4.266 usec = 234,375 kHz

So what I did wrong?

Thank you very much

Solved! Go to Solution.

- Labels:

-

ADC

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-02 06:13 AM

So now it is solved.

everything above about Tconv (sampling time) is corect. And because the clock I used is adc_sclk, so no DIV in ADCx_CCR register has effect on sampling frequency - that was probably main mistake I did.

Then if 1 sample takes 566 ns, then when I measure on all 3 channels, so measure period of first channel is 566*3 ns. And no another div has effect on this period...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-01 04:05 AM

if i see it right way....

you set 30M div 127 -> 4,2 us clock (very slow...) x 17 adc cycl. -> 71 us

you see 58 us , what would be 4,2 us x 14 adc cyc. , maybe you set 2.5+8.5 = 11 and switching channels cost some extra time.

so at first use div 10 , not 128 , and check speed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-01 05:24 AM - edited 2023-11-20 04:14 AM

When I set div (PRESC in ADCX_CCR) to 10:

Then I can measure that 600 samples takes 1.6 ms => 1samples/2.66 usec

But theoretically it should be: 30Mhz/10= 3Mhz => 333 nsec ?!?

When I measure only 1 channel - it also takes 2.66 usec - so no extra cycles are needed to switch channels!

Also I am not sure if Tconv is dependent on PRESC in ADC3_CCR. From datashet I think it is not dependant:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-01 05:48 AM - edited 2023-11-20 04:14 AM

>But theoretically it should be: 30Mhz/10= 3Mhz

it should be + it is so. 333ns * 8 adc cyc. -> 2.6us

the adc still needs some cycles at this clock, to do his job.

+

>From datashet I think it is not dependant:

my ds thinking different:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-01 05:57 AM

>it should be + it is so. 333ns * 8 adc cyc. -> 2.6us

where did you take 8 adc cycles?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-02 04:42 AM

why 333* 8 adc cycles? where is written it should be 8? did you just put it there so that it would come out :) ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-02 06:13 AM

So now it is solved.

everything above about Tconv (sampling time) is corect. And because the clock I used is adc_sclk, so no DIV in ADCx_CCR register has effect on sampling frequency - that was probably main mistake I did.

Then if 1 sample takes 566 ns, then when I measure on all 3 channels, so measure period of first channel is 566*3 ns. And no another div has effect on this period...

- Differential ADC measurment with Zephyr (STM32H563RG) in STM32 MCUs Embedded software

- How to change VSO0 to VSO1 in RCC? in STM32 MCUs Boards and hardware tools

- BLE Connection Interval in STM32 MCUs Wireless

- STM32G030F6P ADC Frequency in STM32CubeMX in STM32CubeMX (MCUs)

- HSO ADC config in STM32 MCUs Motor control