- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Boards and hardware tools

- Re: STM32GO controller PWM Generation issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32GO controller PWM Generation issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-11 4:45 AM

- I'm trying to generate PWM signal using [ TIM3 channel 3] in NUCLEO-G071RB Eval board.

- Time period is 28 microseconds and width are 3 microseconds.

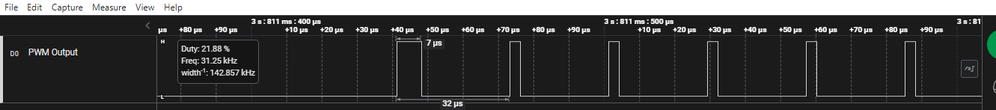

- As you can see in the below [image 1 ]only the first pulse is different or corrupted, which gives 32 microseconds time period and width are 7 microseconds .

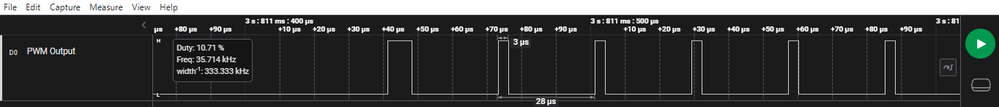

- From the second pulse , we are able to get the expected pulse as shown below [image 2] Time period is 28 microseconds and width are 3 microseconds.

- Same behaviour is observed in STM32Cube_FW_G0_V1.6.0 package code, given by STM32 Timer PWM output example code.

Solved! Go to Solution.

- Labels:

-

ST boards

-

ST-Link

-

STM32G0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-06-06 4:54 AM

Hello @waclawek.jan, @Denial1, @TDK,

This behavior is now noted in Readme files of all HAL TIM examples calling HAL_TIM_PWM_ConfigChannel() with the output channel configured in PWM1 mode:

TIM_6Steps,

TIM_Asymetric,

TIM_CascadeSynchro,

TIM_Combined,

TIM_ComplementarySignals,

TIM_Dithering,

TIM_DMA,

TIM_DMABurst,

TIM_ParallelSynchro,

TIM_PrescalerSelection,

TIM_PWMOutput.

The note is the following:

In this examples, the output channel is configured in PWM1 mode meaning that in up-counting mode, channel 1 is active as long as TIMx_CNT < TIMx_CCR1. As, in the function HAL_TIM_PWM_Start* function, the output channel is enabled prior enabling the timer's counter a timing difference might be observed on the first generated PWM. This difference corresponds to the delay - in term of number of CPU cycles - between the channel enable and the counter enable in the HAL_TIM_PWM_Start* function.

Thank you!

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- « Previous

-

- 1

- 2

- Next »

- Speed Feedback error in STM32 MCUs Motor control

- STM32U083 LCD Controller generates unexpected High Voltage (5V) - and kills its own GPIO pins in STM32 MCUs Products

- SD-card Works in 1-bit mode but it does not work in 4- bit mode. in STM32 MCUs Embedded software

- Motor Control Workbench: Regarding the working & modification of generated code in STM32 MCUs Motor control

- STM32CubeMX v6.13.0 generates broken CMake project files for STM32U5 devices in STM32CubeMX (MCUs)