- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- The program stops (without a breakpoint) at an une...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

The program stops (without a breakpoint) at an unexpected code point during startup

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-15 4:33 AM

I am currently developing software for STM32H7 processors. For this I use the current development environment from Keil (uvision 37.0.0) and Cubemx 6.4.0.

I created an "empty" project for the Nucleo Board STM32H743ZI with Cubemx. In it I only activated one property:

SystemCore/COREX_M7/CPU DCache : Enabled

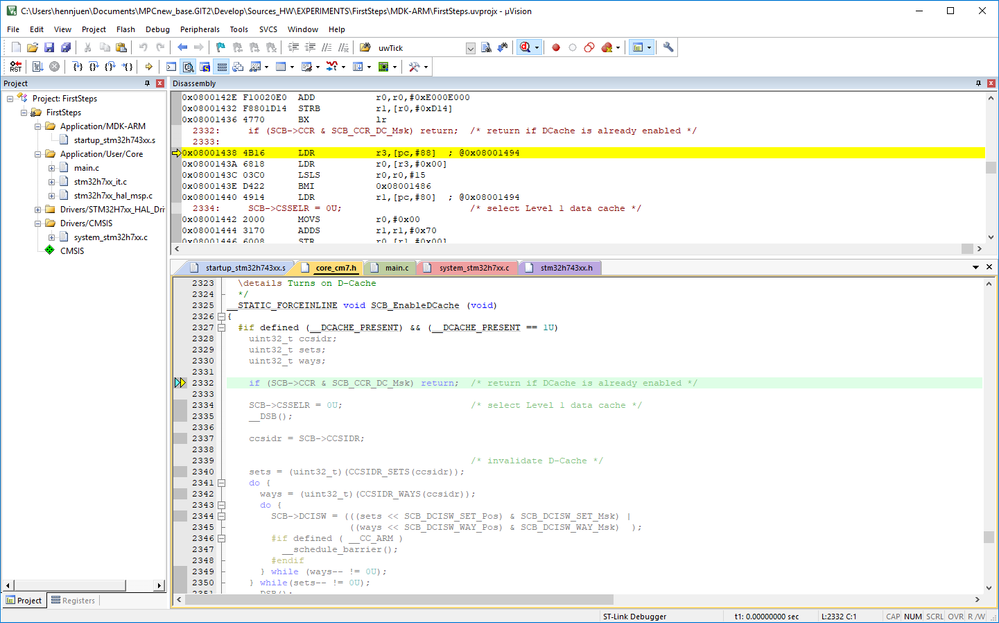

When I compile and upload the generated code I have a strange phenomenon: The program doesn't stop at __Main in the startup-code and also not at HAL_Init() in main.c, but it stops in core_cm7.h in the line:

if (SCB->CCR & SCB_CCR_DC_Msk) return;

But I didn't set a breakpoint there!

My question is about this unwanted "stopping effect" during start phase. The example above is the easiest to reproduce and demonstrate the problem. In fact, I'm working on another project, but that's where this effect degenerates. Sometimes I have to press the F5 key 4 times before the program finally gets to main. This is unbearable in the long run. Does anyone know this effect and has a workaround for it?

- Labels:

-

Debug

-

Keil

-

STM32CubeMX

-

STM32H7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-15 6:07 AM

Using Keil, H7 and Nucleo-H7 boards, and NOT having these issues here.

Would suggest looking more closely at clock and PLL settings, along with VOS settings, and whatever is happening in SystemInit()

Check HSE_VALUE define

These are H743ZI or H743ZI2 boards?

You can uncheck "run to main()" and step in from the beginning.

Do the board examples build and function properly?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-15 1:21 PM

just...about problems, i had :

- disable any watchdog ;

- check, LSE , low speed clock, is on high drive level (or disable it at all, if not needed)

- check, BOOT0 is not active, or gets any spike, so bootloader will start and spoil your program, because it tries to boot ...

- be shure, VCC starting from zero (i made a 470r parallel to VCAP , core voltage ; to set clear start condition)

- then H7 should start always reliable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-15 1:28 PM

VCAP, and BOOT0 shouldn't be a cause of failure on NUCLEO-H743ZI(2) boards.

For extra slow supply rise times, perhaps a thresholding POR circuit

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-15 3:04 PM

Probably not a problem, but you are using an old CMSIS-Core(M) version. At least this old:

https://github.com/ARM-software/CMSIS_5/commit/8ced160cc8362da0fdd794a3e87275b15416b287

> uvision 37.0.0

Why are you inventing version numbers? The current version is v5.37.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-16 12:01 AM

Thanks all for the efforts!

@Tesla DeLorean: It is a H743ZI. The board usually shows no problems. Things get weird when the D-cache is activated.

@Thank you for the starting points. That seems to become a complicated thing.

@Piranha: Sorry, I forgot the 5 in the version number (MDK-ARM Essential Version: 5.37.0.0)

Ok, maybe that's asking a bit too much: If you create a new, empty project for the Nucleo H743ZI board and only turn on the D-cache, will only I have the effect?

- Debugger steps and runs slowly in STM32CubeIDE (MCUs)

- Cannot start RTOS-aware debug session using J-Link in STM32CubeIDE for Visual Studio Code (MCUs)

- Debugging program in external flash XIP mode STM32N6 in STM32CubeIDE (MCUs)

- CubeIDE - How can I Debug Step into functions located in ITCM? in STM32CubeIDE (MCUs)

- STM32H7B3I-EVAL and M2 macOS, new to STM, Example project does not run in STM32CubeIDE (MCUs)