- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- STMcubeMX: TIM3 => ADC1 => DMA1_CHANNEL1 => IRQ

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STMcubeMX: TIM3 => ADC1 => DMA1_CHANNEL1 => IRQ

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-14 6:15 AM

I now try to build such a system using STM32CubeMX/HAL - but with greater problems.

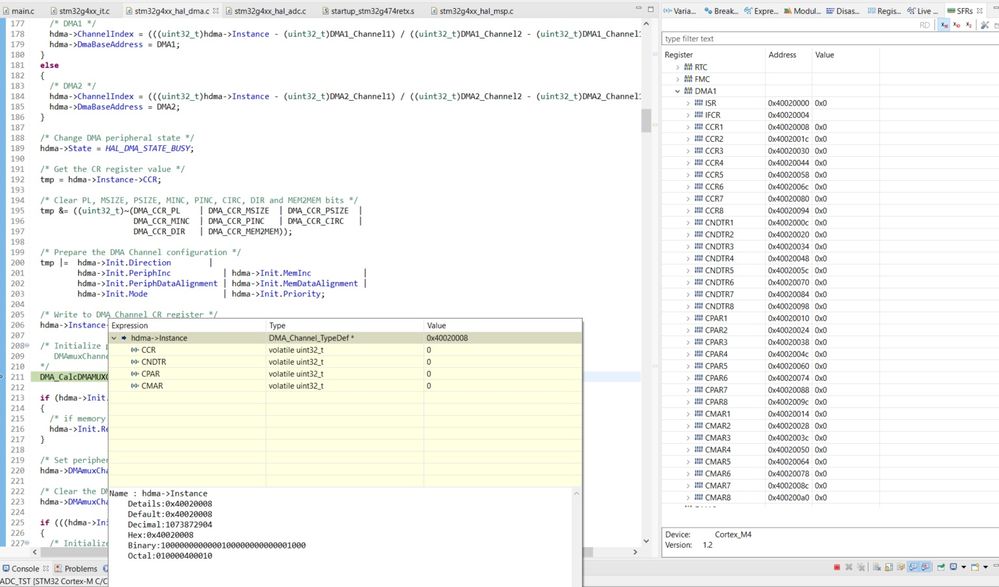

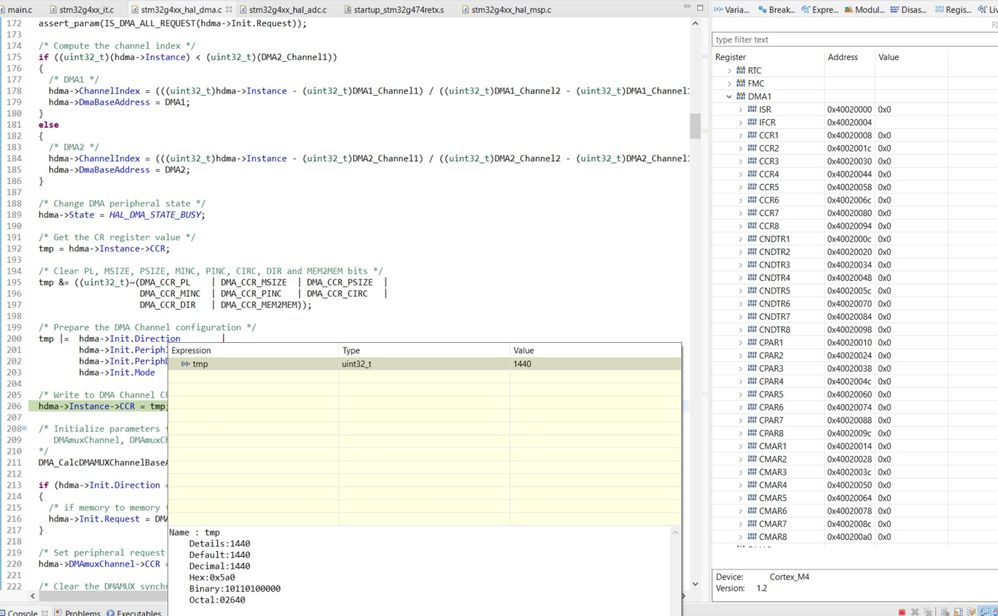

Now writing to hdma->Instance->CCR fails, when I step

into MX_ADC1_Init(),

into HAL_ADC_Init(&hadc1),

into HAL_ADC_MspInit(hadc),

into HAL_DMA_Init(&hdma_adc1)

to the line hdma->Instance->CCR = tmp;

tmp has the value 0x5A0, hdma->Instance->CCR before an after execution of this line the value 0.

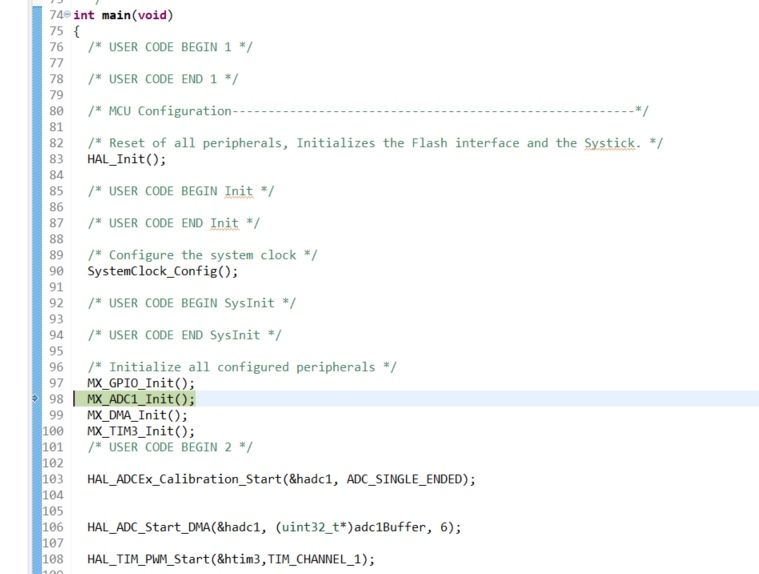

Has the DMA1-Clock to be enabled for writing to DMA1->CCR?

If so, the STM32CubeMX generated siftware will never work, because this Clock will be enabled

inside MX_DMA_Init(), which will be called after MX_ADC1_Init()?

Solved! Go to Solution.

- Labels:

-

ADC

-

Bug-report

-

DMA

-

STM32CubeMX

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-14 6:20 AM

Hello @ULehm.1 ,

Thanks for your post.

This is a known issue with CubeMX v6.3.0: the MX_DMA_Init() shall be called BEFORE any other peripheral initialization when DMA is used.

This issue will be fixed in the coming releases of CubeMx (see this post for more details).

When your question is answered, please close this topic by choosing Select as Best. This will help other users find that answer faster.

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-14 6:20 AM

Hello @ULehm.1 ,

Thanks for your post.

This is a known issue with CubeMX v6.3.0: the MX_DMA_Init() shall be called BEFORE any other peripheral initialization when DMA is used.

This issue will be fixed in the coming releases of CubeMx (see this post for more details).

When your question is answered, please close this topic by choosing Select as Best. This will help other users find that answer faster.

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-14 7:46 AM

> Because my bare metal version of a ADC1+DMA1+DMA1_CHANNEL1+DMAMUX+TIM3 System will not work,

Just get it working. Post what you get, maybe in a new thread.

What benefit you gain from clicking?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-29 6:35 AM

> What benefit you gain from clicking?

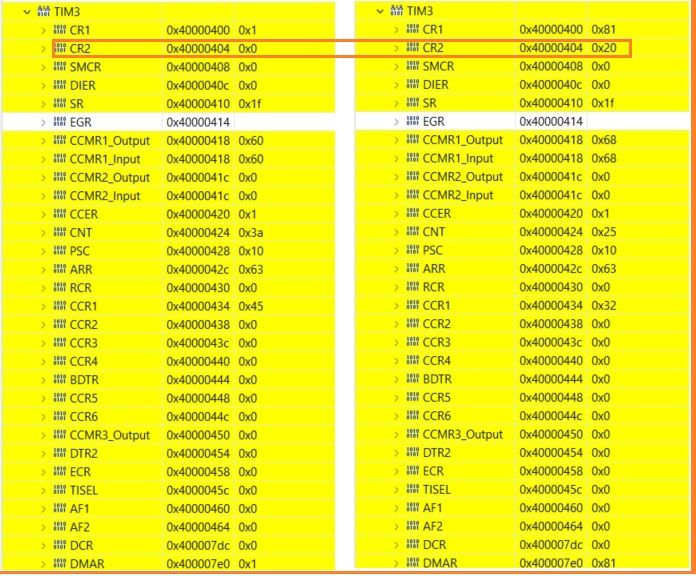

Intention was to compare the SFR contents of the bare metal version with the "clicking" version

and throw an eye on the differences - with success!