- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Re: LwIP problems from code generated via STM32Cub...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LwIP problems from code generated via STM32CubeMX (SMT32H7)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-03 04:55 AM

Hello,

I seem to be having some problems with the code generated via STM32CubeMX on the NUCLEO-H743ZI development board. I want to configure it to run on LwIP/RAW API. I can create such a configuration for its close relative: the NUCLEO F767ZI development board. In the latter case I take the following steps:

- Set the HCLK to 216 MHz (clocked from the HSI);

- Enable the ETH peripheral, set it to RMII mode, and set ETH_TXD0 and ETH_TX_EN pins to PG13 and PG11 (others are mapped appropriately);

- Set the PHY address to 0 in ETH Configuration>General: Ethernet Configuration

- Enable the LwIP middleware;

- Enable ICMP (LWIP_BROADCAST_PING and LWIP_MULTICAST_PING in LwIP Key Options>IPMP Options). This step is not necessary, although it helps to determine if all is well with the device.

After I generate the code, I add an extern variable to my main.c to be able to track whether the device has obtained an IP address:

/* USER CODE BEGIN PV */

/* Private variables ---------------------------------------------------------*/

extern struct netif gnetif;

/* USER CODE END PV */Moreover, I add the standard LwIP/RAW IP callbacks t the main loop:

/* Infinite loop */

/* USER CODE BEGIN WHILE */

while (1)

{

/* USER CODE END WHILE */

/* USER CODE BEGIN 3 */

ethernetif_input(&gnetif);

sys_check_timeouts();

}

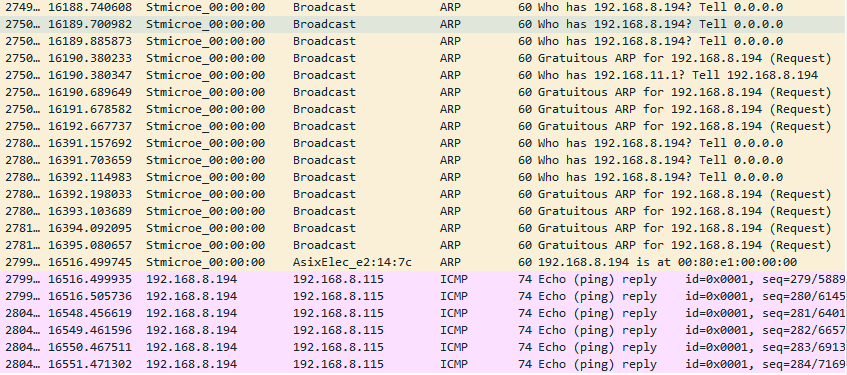

/* USER CODE END 3 */This code works well and I am able to get an IP address (I can determine it frome the gnetif->ip_addr field), I can see all the proper ARP request in WireShark and I am able to ping the device:

Herein, I am filtering only the traffic from/to the appropriate (STM32) MAC address 00:80:E1:00:00:00.

For the NUCLEO-H7432ZI board, I essentially follow the same steps, with a couple of minor deviations:

- Set the HCLK to 400 MHz (clocked from the HSI);

- Enable the ETH peripheral, set it to RMII mode, and set ETH_TXD0 and ETH_TX_EN pins to PG13 and PG11 (others are mapped appropriately);

- Enable the CPU DCache (under Cortex_M7 Configuration)

- Enable the LWIP middleware

- Select LAN8742/LAN8742 as the Driver_PHY (under LwIP>Platform Settings)

- Enable ICMP (LWIP_BROADCAST_PING and LWIP_MULTICAST_PING in LwIP Key Options>IPMP Options).

I change the code in main.c appropriately as for the F7 example. Moreover, I edit the linker file to partition the RAM from 0x24000000 to 0x2407FFFF (there is an instruction in ETH>Parameter Setting to do so in order to get the ETH peripheral working).

If I upload this (nearly identical) build to the NUCLEAO-H743ZI board, I get no network activity (No ARP requests to get an IP address.

Now I know that the issue is somewhere in the STM32CubeMX generated configuration. The hardware itself is good. There is an example of a LwIP HTTP server in STM32Cube_FW_H7_V1.1.0 which works just fine if I upload it to the board. The LwIP_HTTP_Server_Netconn_RTOS example in STM32Cube_FW_H7_V1.1.0 is somewhat different: it uses a RTOS and the Netconn API. For my application I want to stick with Raw API (and no RTOS). So my question would be, what am I missing in my microcontroller configuration?

Solved! Go to Solution.

- Labels:

-

Ethernet

-

STM32CubeMX

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-15 12:51 AM

Hi Pavel,

Thanks. I have built without errors and it runs OK.

At least I am a bit further on in my understanding of how to build an HTTP webserver. but

I do wish that there was a working H743 project to investigate!

Chris

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-15 04:42 AM

FINALLY!!!!!!! Now there is.

I imported the STM32Cube_FW_H7_V1.5.0\Projects\NUCLEO-H743ZI\Applications\LwIP\LwIP_HTTP_Server_Netconn_RTOS\SW4STM32\STM32H743ZI_Nucleo into cubeide v1.7.0

and the H743ZI2 nucleo - worked first time no mods at all.

Now at least I can study the operation. Hope this helps someone!

Chris

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-23 11:00 PM

Hello,

can you please tell me, how did you activate the ETH_IRQHandler(), because i cant call this unless I use Lwip with RTOS

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-24 12:01 PM

Enable the necessary interrupts in ETH peripheral, enable the ETH peripheral in NVIC and set up the DMA descriptors correctly.

About that "perfectly working solution"... It's running the whole IP stack from interrupts, which also means you have to disable interrupts to call any lwIP function from non-interrupt code. And disabling/enabling I-cache is just a complete nonsense.

- « Previous

- Next »

- Possible Bug in STM32CubeMX v6.13.0 in STM32CubeMX (MCUs)

- Code generation problem for FileX in STM32CubeMX (MCUs)

- How create STM32CubeCLT CPP Project with VS code in STM32CubeMX (MCUs)

- Error occurred while regenerating the project in STM32CubeMX 6.13.0 after adding a custom folder path. in STM32CubeIDE (MCUs)

- Validation on target stuck? in STM32CubeMX (MCUs)