Does DFSDM limit SYSCLK frequency? (the problem)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-30 12:33 PM

I am trying to set up DFSDM clock for STM32H7A3VITx and external 10MHz Manchester-encoding modulator using CubeMX.

Since Manchester requires DFSDM clock at least 6x higher than modulator clock, minimum clock frequency is 60MHz.

The only two *active* clock source options are PCLK2 and SYSCLK. PCLK2 cannot be faster than 44MHz (otherwise CubeMX protests) so that leaves me with just one option: SYSCLK.

However, maximum allowed DFSDM clock, depending on Vcore, is 140MHz (DS13195, Table 23, p.84) so I would have to lower SYSCLK.

It seems that clock faster than allowed may cause filter glitches.

Please advise.

Btw, CubeMX does not object to DFSDM clocks higher that 140 MHz while it probably should.

Solved! Go to Solution.

- Labels:

-

DFSDM

-

Documentation

-

RCC

-

STM32CubeMX

-

STM32H7 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-02 2:15 AM

> PCLK2 cannot be faster than 44MHz (otherwise CubeMX protests)

PCLK2 and all APB buses can go up to 140 MHz and CubeMX doesn't limit it either. Read the datasheet - the 44 MHz limit applies only to the VOS level 3.

> CubeMX does not object to DFSDM clocks higher that 140 MHz while it probably should.

Indeed this limit seems to be missing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-31 11:03 PM

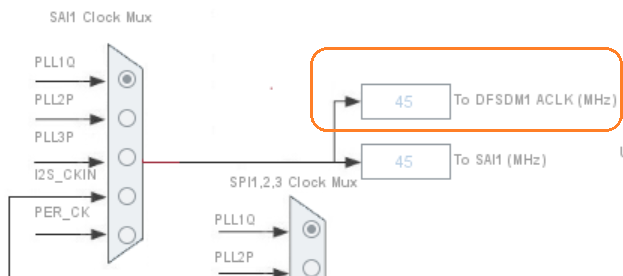

For the output clock source audio (SAI) clock can be used but I guess this does not solve the problem since it is the output clock only (ACLK), not the internal DFSDM clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-02 2:15 AM

> PCLK2 cannot be faster than 44MHz (otherwise CubeMX protests)

PCLK2 and all APB buses can go up to 140 MHz and CubeMX doesn't limit it either. Read the datasheet - the 44 MHz limit applies only to the VOS level 3.

> CubeMX does not object to DFSDM clocks higher that 140 MHz while it probably should.

Indeed this limit seems to be missing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-02 2:29 AM

Ach, that is right, max PCLK2 depends on Vcore as well. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-03 1:06 AM

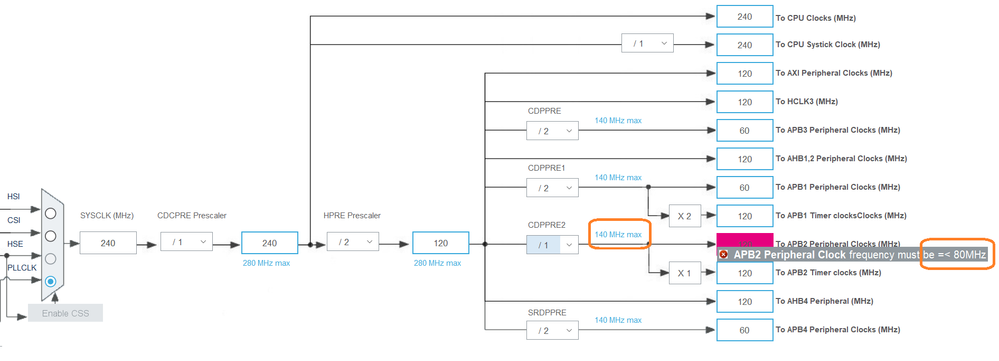

Right, this does not seem correct - see the screen shot.

According to DS13195, Table 23 all APBs have the same limit 140MHz @VOS0.

CubeMX ver 6.2