- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Why do I miss a missing sample from time to time?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why do I miss a missing sample from time to time?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-15 04:01 PM

Hello,

I need to sample 2 signals simultaneously at a rate close to 1MSPS on 16 bits.

On a Nucleo-H743ZI2 board, I thus configured ADC 1 and 2 in Dual regular simultaneous mode, 1.5 Cycle between sampling phases, only one single conversion on each ADC. Sampling is triggered by timer6 at 1MSPS and DMA is used to collect the data (care has been taken about the cache!). ADCs are clocked by PLL2P at 143 MHz which is dived by 4 to reach 35.75 < 36 MHz (from datasheet). With this configuration, I was expecting to be able to sample at a minimum of ~36 MHz / (1.5 cycles + 8.5 cycles) = ~3.6MSPS (from en.STM32H7-Analog-ADC_ADC.pdf). In the worst case it could go down to 3.1 MSPS (I still don't know what the 1.5 Cycle between sampling phases precisely mean in the case of dual ADC mode)

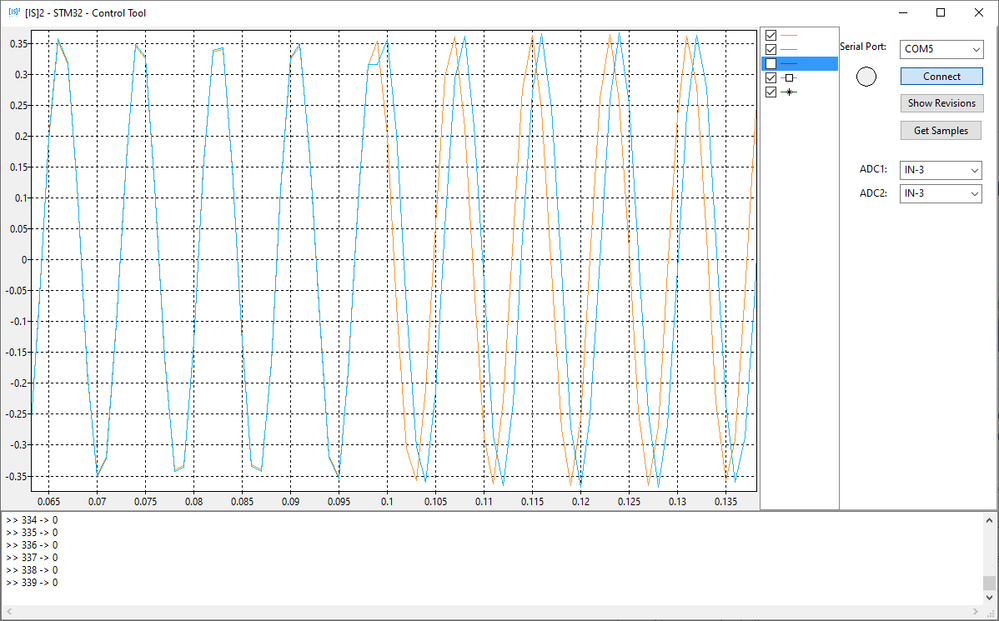

For debugging I sample the same pin, namely PA6 which is connected to ADC1 IN3 and ADC2 IN3. And I discovered that sometimes, ADC2 "jump" one sample.

See attached drawing where ADC1 is in orange and ADC2 in blue, horizontal axis is the time in ms, input signal is a sine wave at 100 KHz.

What could cause this jump?

Sampling rate should already be slow enough, and trying to reduce doesn't seem to improve the results.

There is no other stuff running on the MCU while doing the acquisition (just a UART, which should not be in used during that time)

Thanks for any advice/suggestion....

Jylo

- Labels:

-

ADC

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-15 05:44 PM

without code, difficult to guess your issue,

with code is hard to stop my work to check your code...

but generally its your code re-configuring the DMA all the time.

best practice is to use a circular buffer and never reset the DMA function

Set the DMA up once at startup and then either check the buffer length since last read or set the DMA watermark interrupt.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-15 07:31 PM

>>best practice is to use a circular buffer and never reset the DMA function

THIS

Usually as a Ping-Pong type arrangement, where you service the inactive half at the HT and TC interrupt, and keep your hands off the TIM, ADC and DMA

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-16 12:32 AM

Thanks for your replies!

>>with code is hard to stop my work to check your code...

This is why I submitted the question with no code ... ;)

Actually the amount of processing to be done on each waveform takes so much time that a ping-pong architecture is not suitable.

But DMA as a single shot is not the issue.

Slowing down very much the sampling rate, and even the ADC clock did not help.

However, I think I found a fix: I just needed to increase the sampling time of ADC1 compared to ADC2.

Probably meaning that DMA transfer is triggered by the end of conversion of ADC1, not taking care of the status of ADC2 (?!?)

My last configuration is as follow, and it works fine!

- Mode Dual Regular Simultaneous

- ADC Clock (143 MHz) divided by 4

- Delay Between 2 sampling Phases: 1.5 cycle

- ADC1 Sampling Time: 8.5 Cycles

- ADC2 Sampling Time: 2.5 Cycles

- Trigger = Timer 6 (Prescaler = 10-1; Period = 10-1)

CubeMX is a very great tool, but it hides a little too much the details on the HW, making thus difficult to decide how to configure it!

I've not been able to find the right documentation in order to know what to do without iterative guesses...

Thanks

jylo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-16 11:00 AM

Just a quick update...

After digging in the Reference Manual, I've been able to make some links between HAL setup by CubeMX and ADC registers...

Strangely enough, when recompiling the project, the acquisitions were stable, but shifted by one sample between both ADCs (but no more jumps).

Thanks to RM, and long time spent trying to fix it, I got a solution, with only 1.5 cycle sampling time on each ADC and absolutely no delays between the two ADCs.

I can't tell what was wrong... maybe around the configuration of DMA (currently ADC2 is set to Regular Conversion data stored in DR register and it works fine...)

Enough for now.

- STM32CubeIDE doesn't generate code for timer15 for the STM32G070 in STM32CubeIDE (MCUs)

- M95P32 EEPROM driver: multiple EEPROM instances? in STM32 MCUs Embedded software

- STM32L432 LPTIM prescaler behaviour in STM32 MCUs Embedded software

- STM32H7R3 PSSI RDY/DE bug in STM32 MCUs Products

- JLink GDB Server can not run in STM32CubeIDE for STM32WLE5xx in STM32CubeIDE (MCUs)