- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: To measure the external pulse width, which is ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

To measure the external pulse width, which is the best mode in stm32F411 -

Gated Mode Timer or Input Capture Mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-27 03:13 AM

I need to calibrate the internal timer to do ADC sampling using GPS receiver.

The accuracy of measurement is most important (zero or minimum jitter), PPS output of GPS receiver is input.

Thanks in advance

- Labels:

-

ADC

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-27 10:13 AM

I don't quite see, how would you use the Gated mode for this purpose.

There's no problem with input capture, though.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-27 10:48 AM

PWM Input Capture with CH1/CH2 measuring period/duty

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-27 12:22 PM

For PPS outputs typically only one signal edge is important, not the pulse width.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-31 10:49 PM

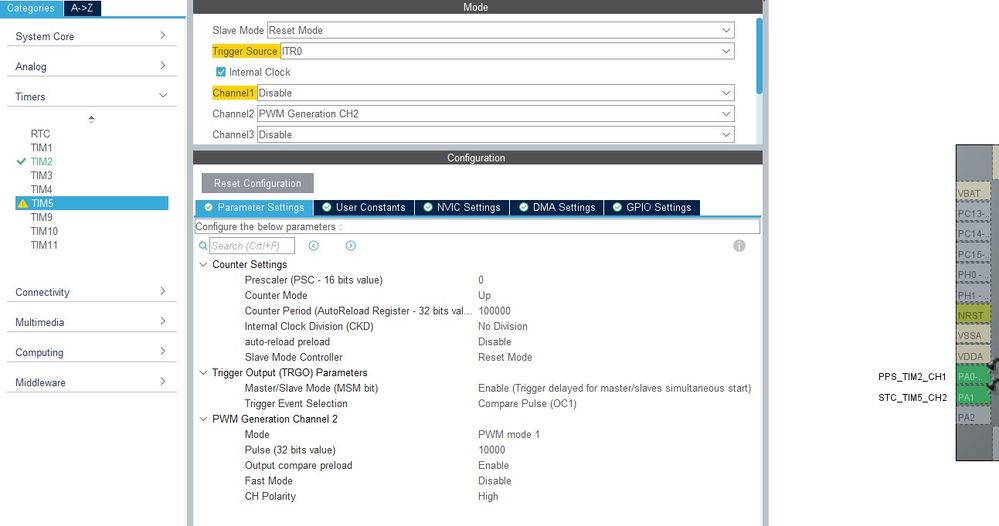

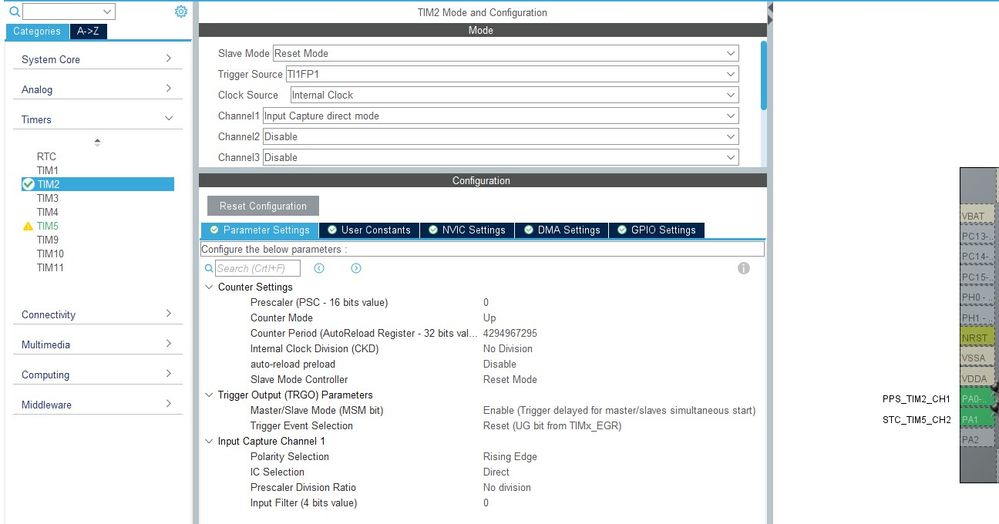

I tried to use slave with gated mode but did not able to generate falling edge event/interrupt of input (PPS from GPS) at TIM2-CH1 (PA0, 32 bits timer). So finally, I have gone with Input Capture direct mode with slave Reset, trigger source with TI1FP1 as attached picture.

ADC start pulse is PWM out in mode 1 from TIM5-CH2 (being nearby pin, PA1), slave with Reset Mode, Trigger source ITR0. I able to get results as expected, sync with gps's pps pulse rising edge, measurement of pps width in 32 bits accuracy with 100 MHz, adjustment of adc sampling rate based on measurement of pps pulse, pulse free running as well when PPS is not available due to some weather or failures. Being used two timers, it give more flexiblity to control the prescaler without effecting each other. The Gated mode must be much simpler than this, but do to configuration issue of event/isr for falling edge, I ignored it. I do not want to use more IOs also.

Thanks to all who provided input to find solution. Still suggestions are welcome to improve further, my objective is minimum IO, processing and disturbances to CPU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-02 01:50 AM

Reset has a lag (delay) after the Input Capture. This is not documented by ST, but found by experimentation to be 2 cycles on some STM32 (e.g. https://community.st.com/s/feed/0D50X00009XkW1oSAF - unofrtunately, Clive's initial post got lost in the forum migration back then).

You may either account for this lag by adding a constant to the measured period, or, maybe better, simply don't use the Reset in Slave-mode controller, just subtract two consecutive captured values from each other.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-02 03:53 AM

Thanks to Dear JW

For pointing out in-built error of Reset Mode. I will take your suggestion.

- Adding of two two cycles in measured period, it may be create MCU series to series.

- I will go with free running ICP (slave disable, triggered source disable), Take the difference of the two CCRs, using below equation in point 3 (got from web). This method avoids if condition check and take same time in all cases.

- ulDifference = ((0x100000000 - tim_ulLastCapture) + ulNewCapture)%0x100000000;

- Do you know any impact of using TIM5-CH2 as PWM out using ITR0 as trigger source to align with ICP input or any better method to this? This alignment is also very crucial for synchronization.

One interesting note - I am using KEIL compiler, found mathematical truncation error, need input how to improve it. I was using Reset mode with below equation

GPS_uwFrequency = (float) SystemCoreClock / TIM2->CCR1;

100Mhz/99645714 = 1.00342572 by compiler,

Calculator (Casio or Window) gives 1.003555456. How to change the equation so compiler and calculator will be same or nearby.

Thanks in advance

T

- Count Encoder in BLDC motor in STM32 MCUs Motor control

- STM32 act as SPI Master and slave for Echo of 1byte Data in STM32 MCUs Embedded software

- STM32f411 crystal in STM32 MCUs Products

- ADC module issues in STM32F429 in STM32 MCUs Boards and hardware tools

- STM32F030T8C6 PWM Not Setting new PWM Value. in STM32 MCUs Products