- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- TIMx Clock Division Configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TIMx Clock Division Configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-09 10:48 PM

Hey, I am trying to understand timers, everything goes nice, but I have a question in my mind.

I am able to set the prescaler and period values according to my purporse, but I can't use the internal clock division effectively.

My TIM2 clock signal is 12 MHz, then I use 11999 as PSC and 999 as ARR, so I expect my timer to count up to 999 in exactly 1 seconds and then reset to 0.

And it does, but the problem occurs when I set Internal Clock Division parameter (from CubeMX) to,for example, 4 ; I expect it to count up to 999 in 4 seconds this time but it does not. It just counts again in 1 seconds.

Is there something wrong in my understanding of this Internal Clock Division thing?

Thanks in advance.

Solved! Go to Solution.

- Labels:

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 12:07 PM

The CKD bits control the divider in the TIx "Input filter & edge detector" block and ETR "Polarity selection & edge detector & prescaler" box. Alas, at least the L4xx manual doesn't actually show the CKD bits going to these blocks. But the CKD bits description under the CR1 register mentions both of these. This is NOT the "PSC" (prescaler) bits that ARE shown in the diagram, which indeed does divide the input clock before going to the CNT register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 01:06 AM

Up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 01:42 AM

Maybe You should try reading the reference manual?

https://community.st.com/s/question/0D50X00009XkWLvSAN/what-is-the-use-of-clock-division-settings-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 02:26 AM

I don't know why you think I did not read the reference manual or did not searched on web and read the post you just shared. I asked this question because existed answers/sources on the internet was not an answer to my question. ( Either they did not consist the information I need, or I was not able to understand. )

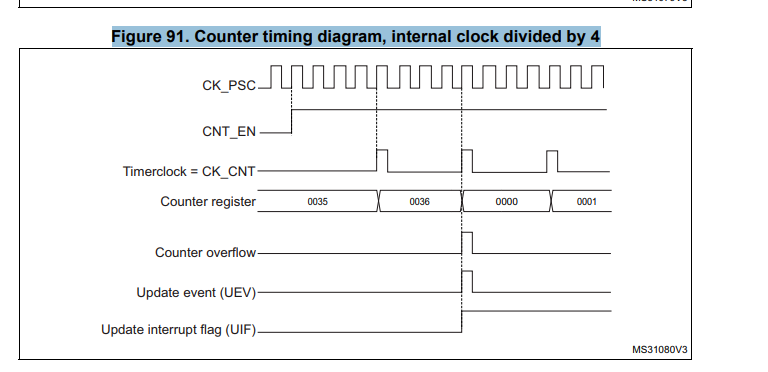

When I look into the reference manual, at page 521 of RM0090, "Figure 91. Counter timing diagram, internal clock divided by 4" shows that;

I understand from this figure that timer should count up by 1 for every 4 clock signal that it receives.

And I just kindly ask that which point I am missing?

Thanks anyway.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 05:57 AM

Up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 08:57 AM

In CubeMX, the "internal clock division" is the clock divider on the timer's input filter. It is NOT a divisor in the timer's clock chain. This is a common confusion. At least in the CubeMX version I am running, for the L4xx processors, the label is "Internal Clock Division (CKD)". The "CKD" is the clue. Look for those bits in the timer CR1 register description, then look at the timer block diagram.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 11:45 AM

Hey, thanks for the answer. It is same "CKD" in f4xx also. So, what does that figure represents than? They draw it like the internal clock division value just scales down the counter frequency. Am I wrong? It look just plain simple from that figure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 12:07 PM

The CKD bits control the divider in the TIx "Input filter & edge detector" block and ETR "Polarity selection & edge detector & prescaler" box. Alas, at least the L4xx manual doesn't actually show the CKD bits going to these blocks. But the CKD bits description under the CR1 register mentions both of these. This is NOT the "PSC" (prescaler) bits that ARE shown in the diagram, which indeed does divide the input clock before going to the CNT register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-10 09:28 PM

Well, then the way they(st) used that figure is not helpful to people instead confusing. Thanks for anwers, have a nice day.

- STM32H7S78 DK switch HSE clock problem in STM32 MCUs Products

- stm32f446vet in STM32 MCUs Products

- ADS1293 sensor interface with STM32nucleo-u083rc board in STM32 MCUs Products

- Problem with DAC+DMA End-of-Transmission Interrupts on STM32L452RET6P in STM32 MCUs Products

- STM32H743 HCLK3 frequency error in Clock Configuration for HPRE=1 in STM32CubeMX (MCUs)