- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Synchronization of SPI and DMA for Block data tran...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Synchronization of SPI and DMA for Block data transfer using DMAMUX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-08 02:17 AM

Hi, I am trying to synchronize a SPI Block data transfer between two MCU's (Ti MSP430 Master, STM32G0 Slave). The idea is to use the DMA to transfer the data to memory and use the DMAMUX to Sync with a timer.

For demonstration, the data is transmitted to USART.

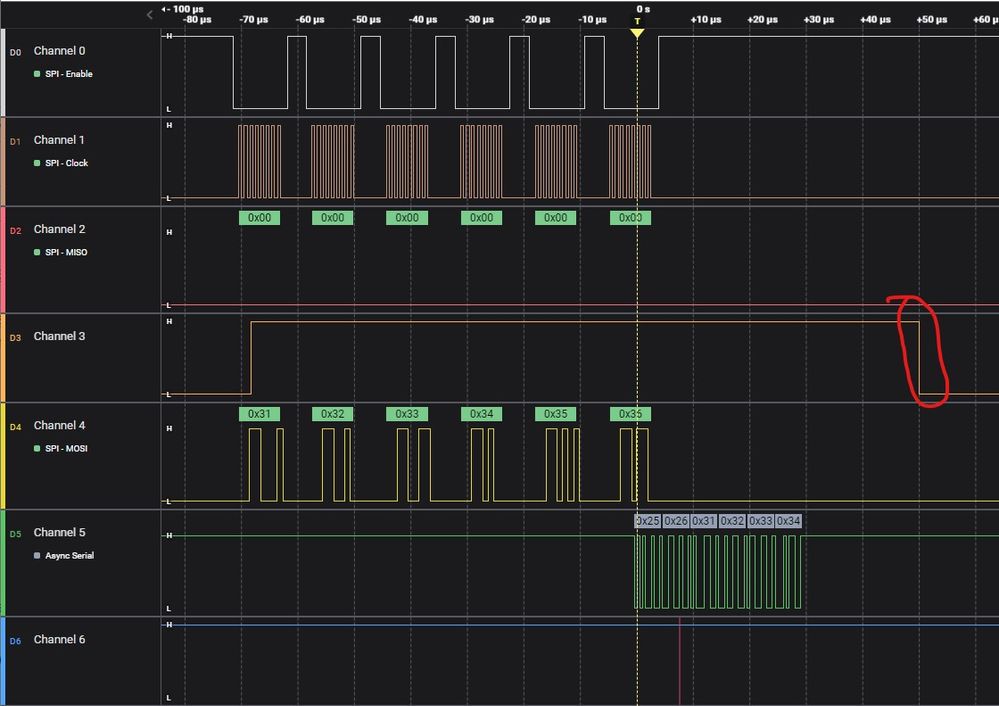

Here is my result:

The red cycle mark the sync point generated by the timer interrupt of LPTIM1.

For testing, a defined pattern with 6Byte is transmitted via the SPI. And you can see that the data is not in sync with the block transmission.

Has anyone an idea how to solve this?

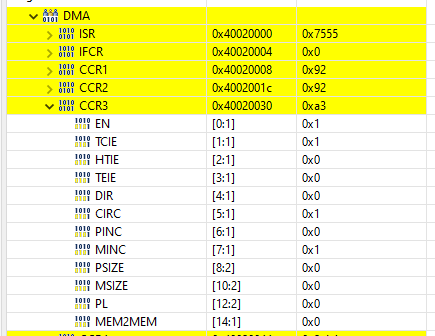

SPI1 is configured to receive the data in Slave mode and use DMA.

DMA Channel 3 is configured to transmit data from SPI1Rx to memory

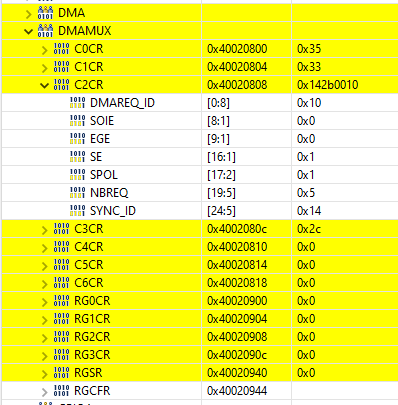

DMAMUX Channel 2 is configured to SPI1Rx synced by LPTIM1

Solved! Go to Solution.

- Labels:

-

DMA

-

SPI

-

STM32G0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-14 06:09 AM

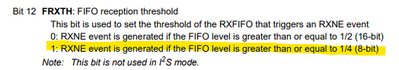

Today I was able to solve the problem by myself.

The solution was to set the FRXTH bit from the SPI configuration.

Now all data is transmitted via the DMA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-08 07:11 AM

Can you draw your desired waveform? Consider using an SPI slave to drive that line if you want each byte to be perfectly in sync.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-10 11:14 PM

Hi, TDK

Sorry I do not understand you. Currently, the Master (MSP430) is driving the communication.

The goal is that the bytes that are send by the MSP will be received in sync by the STM32G0.

Like shown in the picture above the received bytes are shifted by 2 bytes. And that is what I have to avoid.

MSP is sending 0x31;0x32;0x33;0x34;0x34;0x35;0x36

STMG0 has received (DMA TC ISR) 0x25;0x26;0x31;0x32;0x33;0x34

The first 2 bytes are from the last data block.

I want to use the synchronization signal of the DMAMUX raised by the LPTIM1 to solve this problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-14 06:09 AM

Today I was able to solve the problem by myself.

The solution was to set the FRXTH bit from the SPI configuration.

Now all data is transmitted via the DMA.

- USB Microphone in STM32 MCUs Products

- DMAMUX: Chaining of request generators in STM32 MCUs Embedded software

- ADC: DMA of injected conversions does not work, when there are no regular conversions in STM32 MCUs Products

- Synchronize DMA to GPIO transfer on 2 distant MCU by external signal. in STM32 MCUs Products

- Unable to make USBX and FileX working on same sd-card in STM32 MCUs Embedded software