- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Switching time for mux on Opamp

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Switching time for mux on Opamp

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-24 7:34 AM

Various STM32 products have opamps that have a mux in front of it.Ex: STM32G4, STM32F3, STM32H7 series, etc.

If I change the mux input setting using the control status register (OPAMPx_CSR::VP_SEL or VN_SEL), how long does it take for the mux to switch to the new setting?

The datasheet doesn't have this information.

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-04 8:48 AM

Hi @Singh.Harjit ,

Sorry for delay to provide an answer, I was checking for answer with our Experts.

Unfortunately, We don’t have exact values to answer your question "how long does it take for the mux to switch to the new setting?". But you may consider that the switching time of the switch itself is few 10th of nsec to 100th nsec.

However, as the feedback loop of the OPAMP is broken by its nature, it needs some time to become a stable output (close the feedback loop).

This will be limited by the slew rate of OPAMP and condition of the circuit (for example capacitance in the feedback loop).

For example, if one of the GPIOs is 0.1V and another one is 2.9V, OPAMP is configured as voltage follower so Output must jump from 0.1V to 2.9V.

In the particular case of G4 OPAMP in normal mode the rate is 2.5V/us (minimum spec). So to move from 0.1V to 2.9V, the delta is 2.8V: 2.8 / 2.5 = 1.12 => it takes 1.12usec.

==> So switching time is slow enough compared to the OPAMP stabilization time.

Does this answer your question? Or may you still have other related ones?

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-04 8:48 AM

Hi @Singh.Harjit ,

Sorry for delay to provide an answer, I was checking for answer with our Experts.

Unfortunately, We don’t have exact values to answer your question "how long does it take for the mux to switch to the new setting?". But you may consider that the switching time of the switch itself is few 10th of nsec to 100th nsec.

However, as the feedback loop of the OPAMP is broken by its nature, it needs some time to become a stable output (close the feedback loop).

This will be limited by the slew rate of OPAMP and condition of the circuit (for example capacitance in the feedback loop).

For example, if one of the GPIOs is 0.1V and another one is 2.9V, OPAMP is configured as voltage follower so Output must jump from 0.1V to 2.9V.

In the particular case of G4 OPAMP in normal mode the rate is 2.5V/us (minimum spec). So to move from 0.1V to 2.9V, the delta is 2.8V: 2.8 / 2.5 = 1.12 => it takes 1.12usec.

==> So switching time is slow enough compared to the OPAMP stabilization time.

Does this answer your question? Or may you still have other related ones?

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-07 7:00 AM

@Amel NASRI Thank you for the information. It answers my question.

No worries about the time it took to get an answer. I figured that since it wasn't documented, you must have reached out to the design or verification team to see if anyone knew the information and were waiting for a response. Appreciate that!

The information you provided is sufficient - that the switching time is less than 100ns and will be dominated by the opamp's slew rate/gain bandwidth product.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-07 7:51 AM

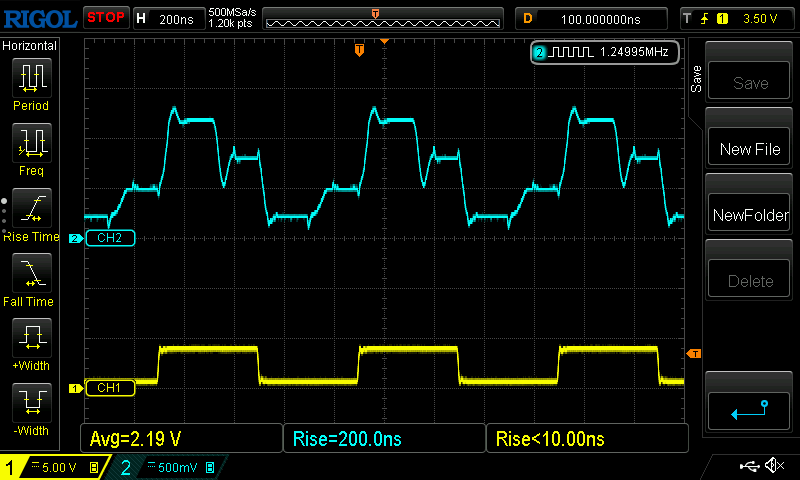

I have a project using stm32G474 nucleo board. The idea is "upconvter" sampling rate of the internal 4 fast - 15 msps DAC using OPAs with input MUX switching. So, 1-st OPA alternatively selects outputs of two DAC's - everything is driven synchronously by Timers chain network. 2-nd OPA - another pair of DACs. And last OPA selects output opa-1 or opa-2 . Switching glitches stop me from developing this into practical design.

Here is a picture:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-07 8:29 AM

Awesome data! Thank you for making time to share it and explain what you did and the issue.

In my application, the opamp is going into the ADC. So, I can adjust the sampling time so that the glitch has settled out.

In your application, I'm guessing you want a sample and hold so that you can use that to sample and hold the opamp output, switch the opamp's mux input, wait for the opamp to settle and then reconnect the sample and hold to pass through the new input.

- Rendering time is abysmal in STM32 MCUs TouchGFX and GUI

- Nucleo STM32C071RB with WS2812b issue in Others: STM32 MCUs related

- SPI Between Two STM32 Boards - Data Not Received in STM32 MCUs Embedded software

- Increasing prescaler on the fly causes the timer to never update. in STM32 MCUs Products

- EVSPIN32G4 driver protection glitching during boot-up in STM32 MCUs Motor control